アナログコンピュータの製作

アナログコンピュータ(EDEQS23)の製作過程の記録

1.構想・実験

アナログコンピュータ試作機 から得た反省を活かした本格的なアナログコンピュータを製作すると思うに至ったのは2023年 のはじめごろであったと思う。それから約半年は、一度も半田ごてを持たず、紙の上での構想 とブレッドボード上での実験に終始した。試作機では予算をどれだけ抑えられるかが最優先であったが、今回は財布のひもを幾分か緩め、微分方程式の解を定量的に評価できる程度の精度は実現したいと考えた。

春時点で決定していた要求項目は次の通り。

- 積分器は10個、乗算器は16個、加算器は6個、係数器は全て10回転のポテンショメータ

- 演算基準電圧と電源電圧の分離

- 基準電圧は高精度電圧リファレンスICにて生成

- 演算増幅器は全てJFET入力オペアンプで、積分器の単体精度は0.1%を目指す

- 演算にかかわる抵抗器は全て許容誤差0.1%の金属皮膜抵抗

- 初期条件モード・演算モード・保持モードを設ける。モード切替はリレーを使わず、電源電圧範囲40Vのアナログスイッチを用いる

- その他、比較器、絶対値要素、飽和要素なども設ける

アナログ計算機のそもそもの仕組みや演算の方法については「演算の理論」で説明してあるので参考にしていただきたい。

受動部品の選定について。積分器は微分方程式を解くのに欠かせないものだが、普通に秋月電子で売ってあるようなフィルムコンデンサは誘電吸収現象・漏れ電流や静電容量の誤差が大きすぎて使いものにならない。漏れ電流が大きいと解の振幅が時間とともに減少するなど誤差の原因となる。当然静電容量誤差も小さいものがよい。それらの要求をクリアできるのは、ポリプロピレンフィルムコンデンサやポリスチレンフィルムコンデンサくらいだが、一般に市販されている単価200円の誤差5%(F級)程度のものでは不十分である。公差は1%くらいに抑えたい。

高速モード用の1μFおよび低速用の1nFについて、

- 許容誤差1%程度

- 1nFについては絶縁抵抗100GΩ以上、1μFについては1GΩ以上

- ただし単価が高すぎない

が最終的な条件となった。様々なコンデンサをかき集めて、ブレッドボード上に仮の積分器と加算器を組み立てて2階微分方程式を解く回路を作り、その解(正弦波)の振幅誤差などをオシロスコープやXYレコーダで試験した結果、最終候補として残ったコンデンサは次の2種である。

- MKP(1μF)/KP(1nF)

- K71-7(1μF)

MKP/KPシリーズはVishayのポリプロピレンフィルムコンデンサで、1μFの方はMKP416(耐圧63V、誤差2%、絶縁抵抗30GΩmax)、1nFの方はKP1830(耐圧630Vdc、誤差1%、絶縁抵抗500GΩmax)である。これらはDigikeyで購入した。誤差や漏れ電流が小さいのは言うまでもない。高速型の場合は誘電吸収(両端子をショートしたあとも電圧が0にならず、たちどころに電圧が回復してしまう現象)が誤差として効いてくるのだが、実験の結果KP1830はその影響もかなり小さいことが確認できた。大変優秀である。1nFにはこのKP1830を使用することに決めた。

問題は1μFである。前述のMKP416の他に「K71-7」が候補に挙がり、そのどちらを使うか決めきれず、長い間悩みに悩んだのだ。

.jpg)

K71-7は旧ソ連製の軍用規格ポリスチレンフィルムコンデンサであり、公称誤差0.5%で絶縁抵抗も十分高いようだ。(海外の人がこのコンデンサの絶縁抵抗や誘電吸収を実測した結果がこちらにある。論文形式の記事もある。公称値はここに記載されており、0.33µF以上の場合の公称絶縁抵抗が5GΩmax。実際はこれよりはるかに高いと思う。) 容量誤差0.5%のコンデンサなんて滅多にお目に掛かれないもので、それが本当であればアナログ積分器のコンデンサとして最適である。比較実験のために早速eBayで0.5µFのものを購入。戦乱渦巻くウクライナより数週間かけて到着した。

.jpg)

その数50個。これが最小購入単位だった。(K71-7シリーズの最大容量は0.5µで1μFのものは存在しない。ゆえに、積分時定数を1sにするためには2個並列にせねばならない。)

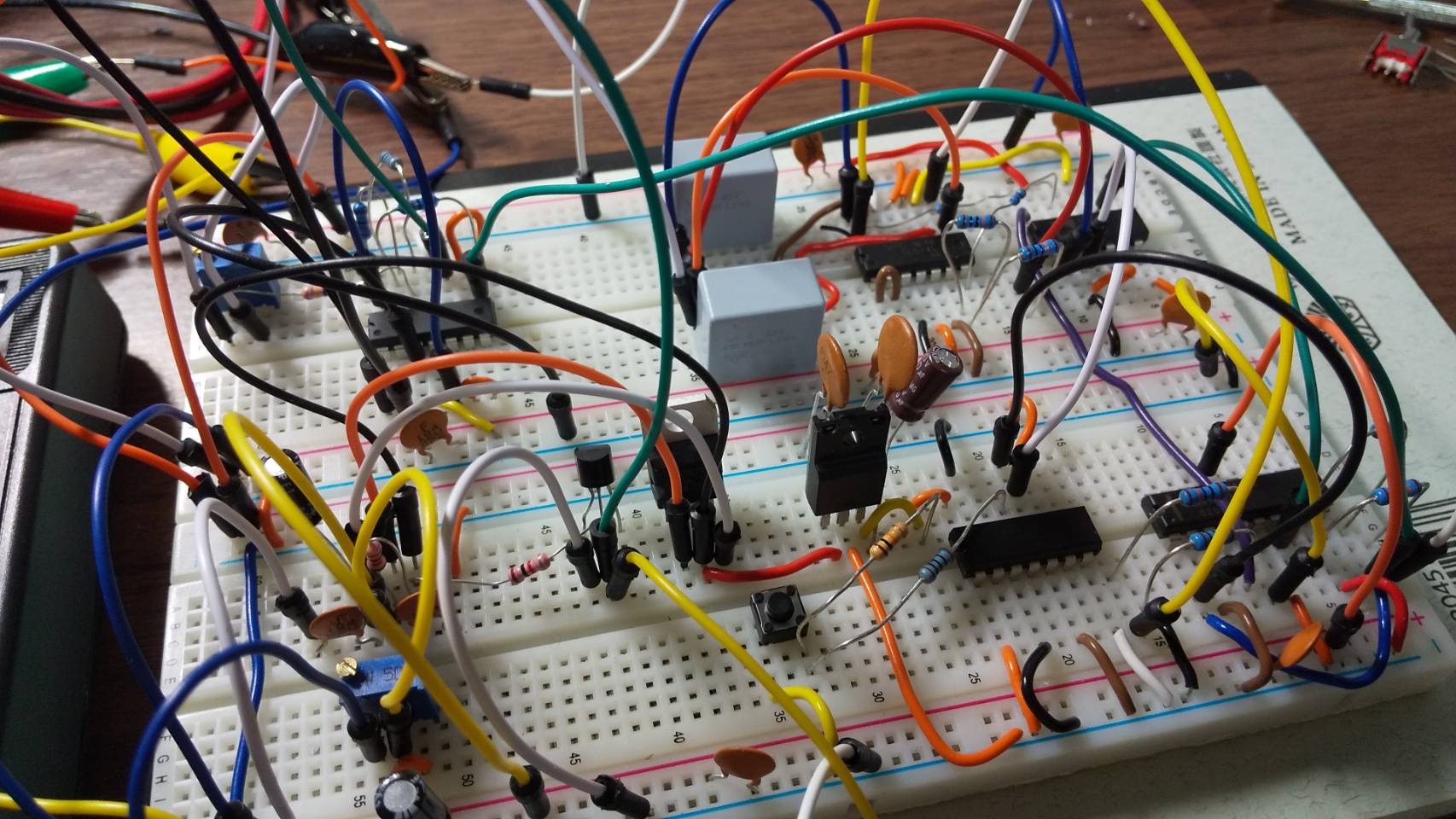

SANWAのデジタルマルチメーターPC7000で容量を測ろうにも、キャパシタンス測定レンジの確度が3.5%rdg±5dgtなのでまともに測れない。こういうときは、十分な確度で精度を計測できている1MΩ抵抗とオフセットをあらかじめ調節されたオペアンプで時定数1sの簡易積分回路を組み、高精度基準電圧を入力して出力に現れる時間比例電圧関数の傾きがどれだけ「1」に近いかみればよい。容量誤差を電圧誤差に変換して計測するわけである。また、漏れ電流の大きさも \(\dot{y}=-y\)の微分方程式を解く回路をブレボで組んで解として得られる\(\sin{t}, \cos{t}\)をXYレコーダに入力して円を描かせ、一定時間後の円の直径がどれだけ減衰しているかをみれば得られる。(サークルテストという。)

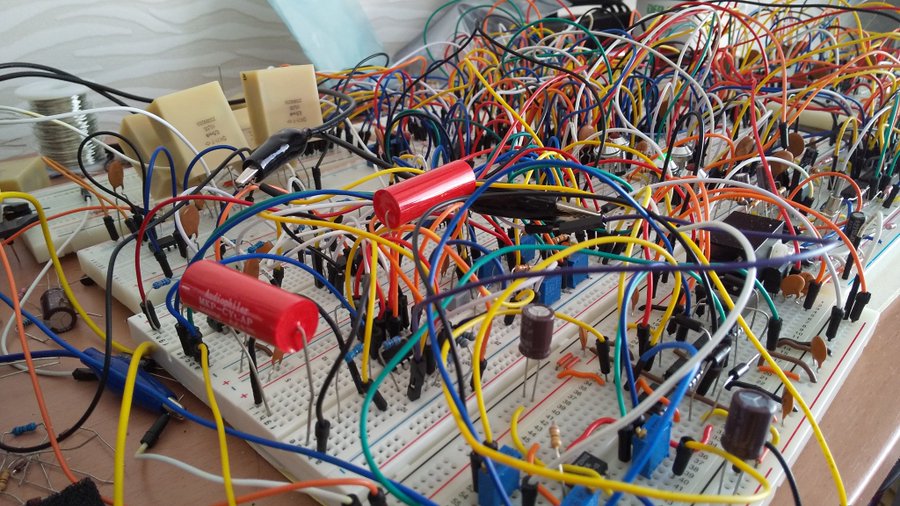

↑仮組みした積分回路

↑サークルテスト中

↑ランプ関数

実験したが、積分精度の総合評価はMKP416が僅差で勝っているようである。だが、K71-7も(精度0.5%とまではいかないものの)かなり健闘しているので全く使い物にならないわけではない。

コンデンサの単価として安いものはK71-7で、予備も含めてある程度まとまった数確保しているが、このポリスチレンコンデンサは外形が大きすぎるという問題がある。MKP416に比べたら5倍はデカい。それを2つ並列となるといたずらにスペースを食うのみである。いろいろ悩んだ末、結局はMKP416を使うことに決定した。

次に重要な素子は抵抗器である。抵抗器は、積分器には入力部や初期条件設定回路として、加算器には入力・帰還部に大量に使用する必要があるため、いくら高精度な抵抗が入手できるからと言って闇雲に高級品を選ぶと総コストが膨大になってしまう。ゆえに、抵抗器の選定においては精度と予算のバランス取りにコンデンサ以上に慎重にならねばならない。当初はAliExpressで安かった公称0.1%の金属皮膜抵抗器の使用を考え、100kと1Mを100個それぞれ購入したが、どう計測しても1%~3%は誤差がある。さすがにこれは使えないので、Digikeyで別の0.1%品を購入した。YR1B1M0CCというシリーズ。100個で5400円。公称温度係数±15ppm/℃。実際の誤差も、そのバラツキも十分小さく、だいたい0.2~0.1%程度に収まっているようである。マルチメーターの測定誤差を差し引いて考えても、中華製のモノよりだいぶ使える。コストパフォーマンスもよさそうなので、それぞれ100個購入した。

いやいや、地味に抵抗だけで1万円かかってますやん、どうすんのよこれ…。しかしこれも自ら選び取った道である。いまさら泣き言言ってもはじまらない。高精度回路を実現するため必要な犠牲だったと自分に言い聞かせるのみ(涙目)

これまで受動素子の選定についての話だったが、次に語るのは演算器用オペアンプの選定。受動素子についてはだいぶ精度にうるさく選定をおこなったので、オペアンプも高精度アンプを多用するのかといえば、そうではない。汎用品で十分である。

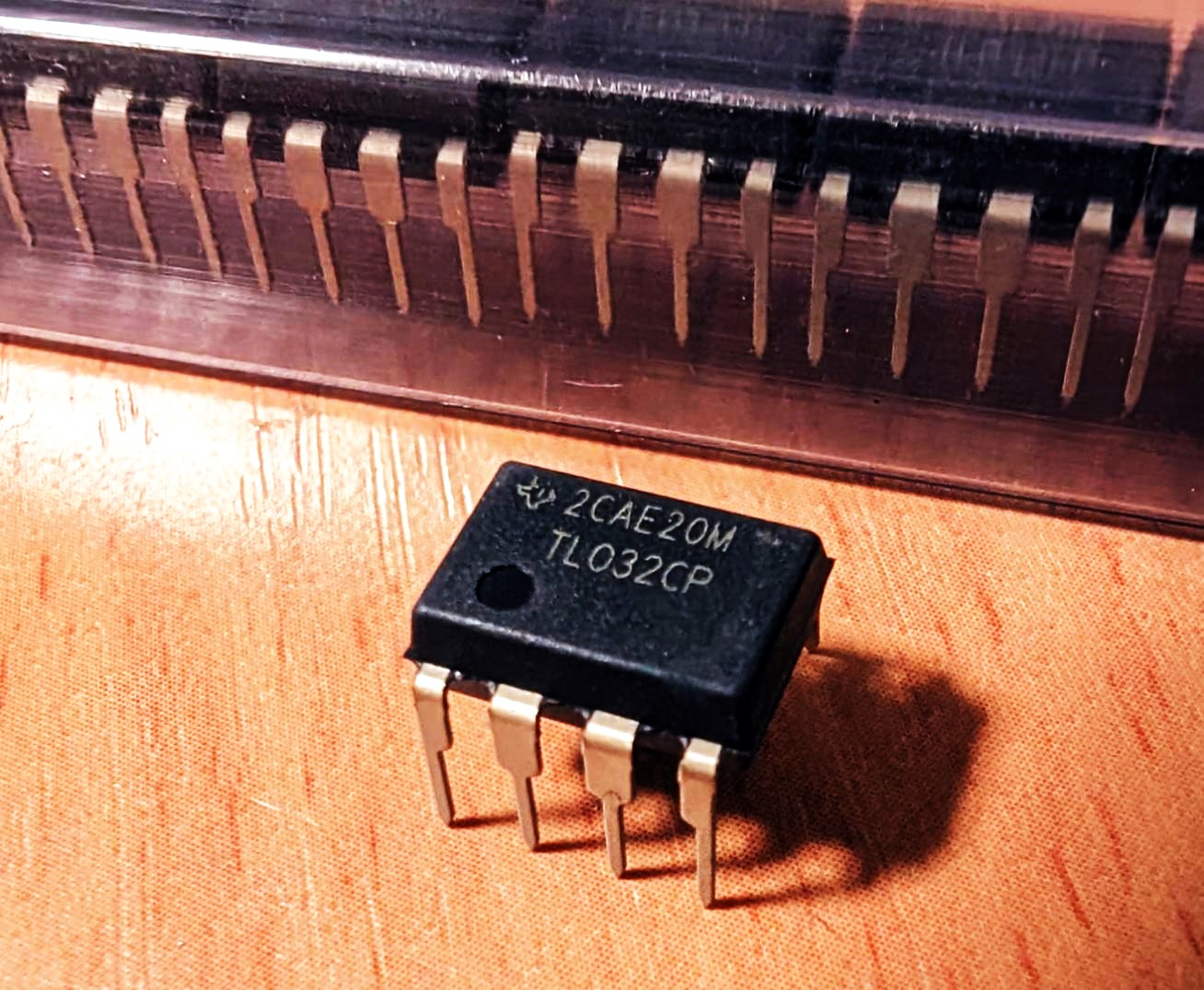

(↑ TL074)

完全な主観だが、アナログ計算用演算増幅器に求められる条件は

- 一に「高入力インピーダンス」(10^12Ω以上)

- 二に「低ドリフト」

- 三四がなくて五に「低オフセット」(ただし10Vフルスケールの場合1桁mV以内であれば十分)

という感じだろうか。(両電源動作、差動入力電圧範囲>20Vは当たり前のことであるから言及していない。)高入力インピーダンスはすべてに優先する必須項目なので、JFET入力のオペアンプがよいだろう。

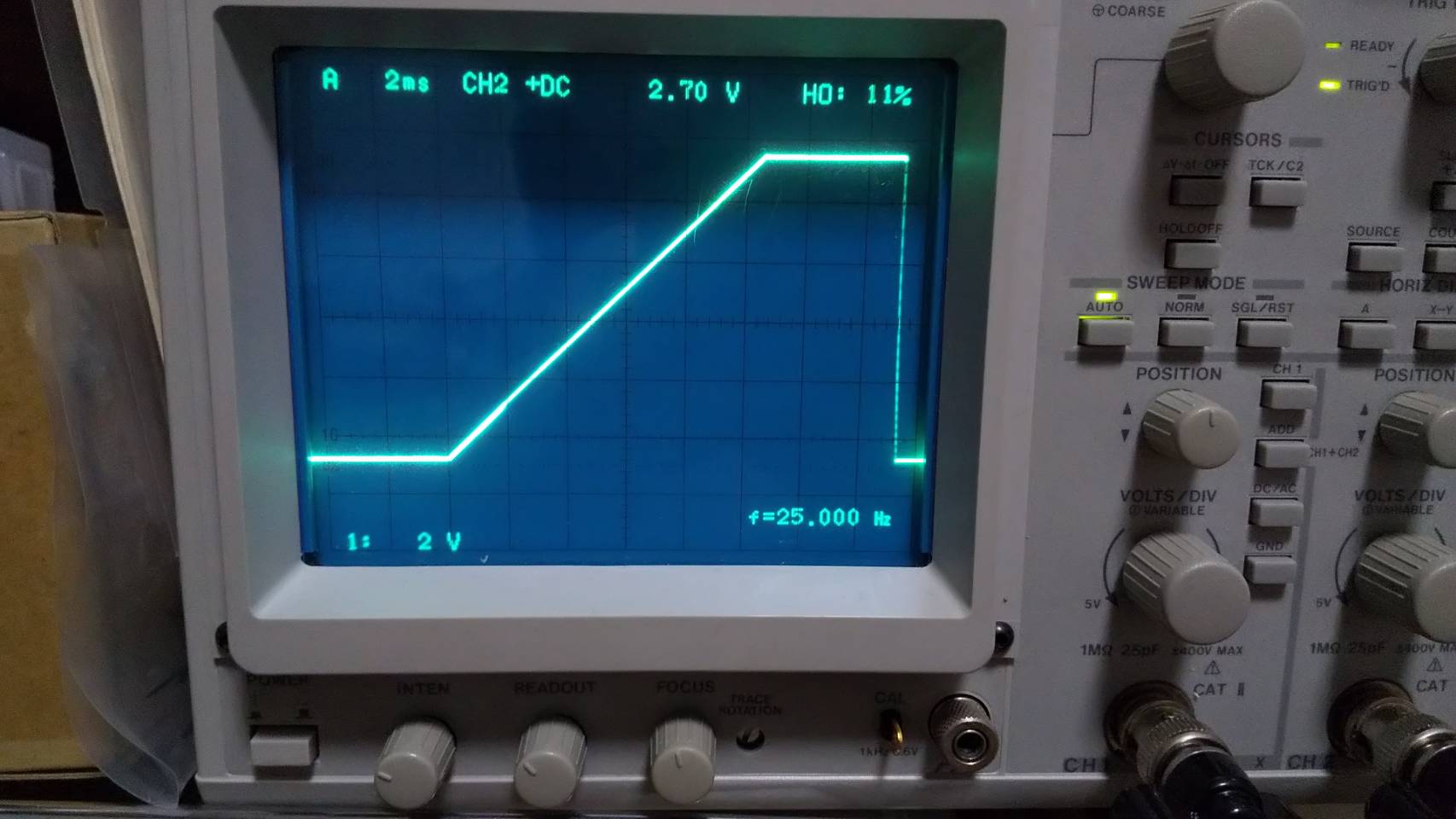

高速モード演算周波数は大抵の場合50Hz~500Hzの間に収まり、高くて数kHz程度であるから周波数特性はほとんど気にする必要がない。たとえオフセット電圧がmVオーダーであっても、トリマ回路を付けて調整すればいいので、必ずしもオフセットがμV以下のオーダーの高級品(単価千円)を数十個買って財布に大穴をあける必要はないのだ。 TL074やTL082など(単価50円)でもいいが、とはいえオフセット電圧が小さいに越したことは無いので、JFET入力オペアンプでは最もオフセットが小さい部類に入るであろうTL032(単価100円強)を積分器・加算器・反転器に用いることにした。オフセット1mV以下だが入力インピーダンスは10^12Ωある。それ以外の要素にはオフセット電圧 3mV typ. のTL074、TL082を用いることにする。 必要があればオフセットヌル回路を付ける。

(↑ TL032)

積分器の回路を決定したら、簡単な線形2階常微分方程式を解く回路をブレッドボードで組めるようになった。以下が減衰振動のシミュレーション(高速モード)を積分器2個、反転器1個で行った様子である。

.jpg)

.jpg)

TRIOのブラウン管オシロ(CO-1302)で解を表示している。アナログコンピュータが完成すれば、多種多様な微分方程式をブレッドボードで組むよりはるかに簡単にシミュレーションできるようになるはず。

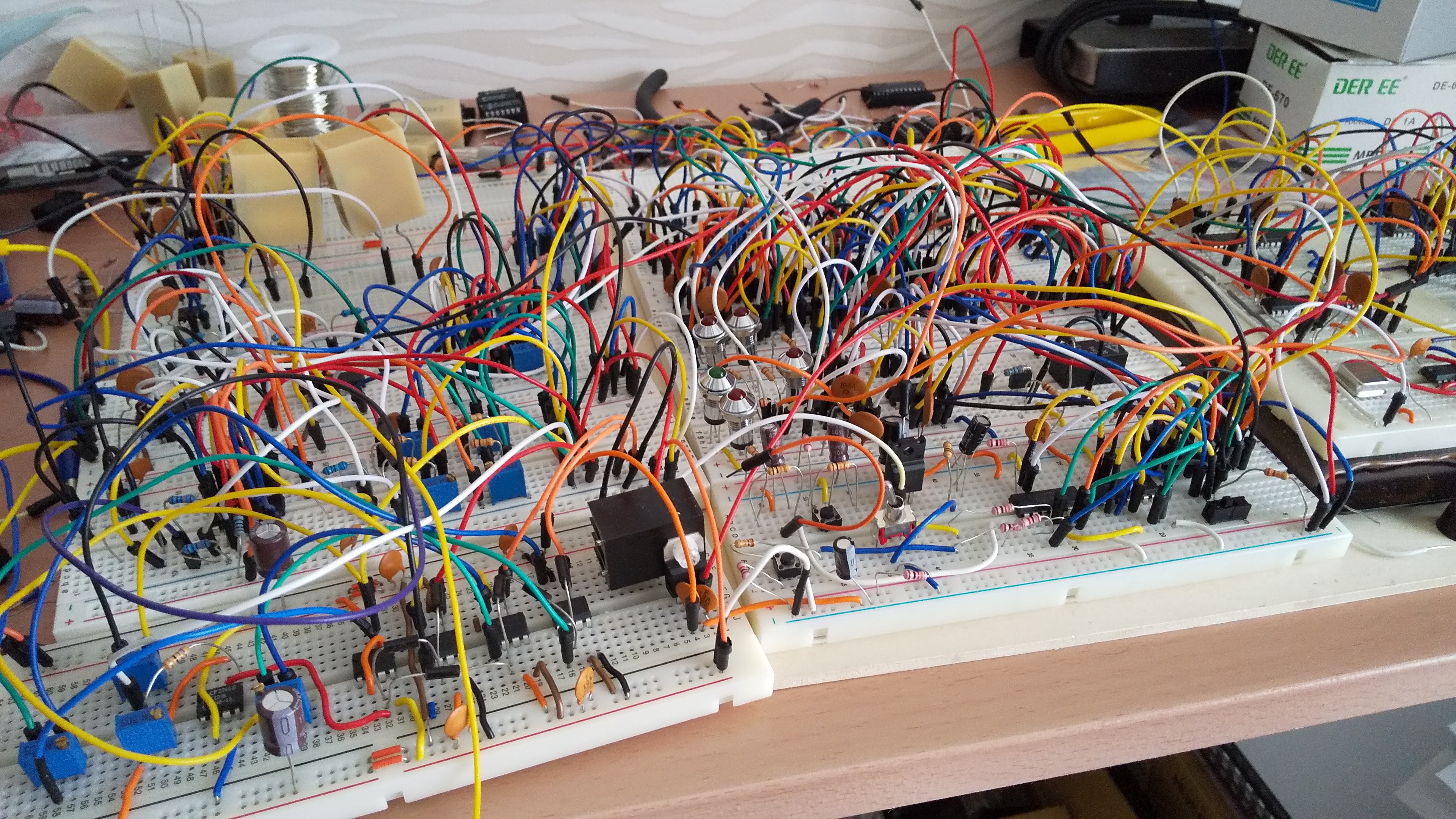

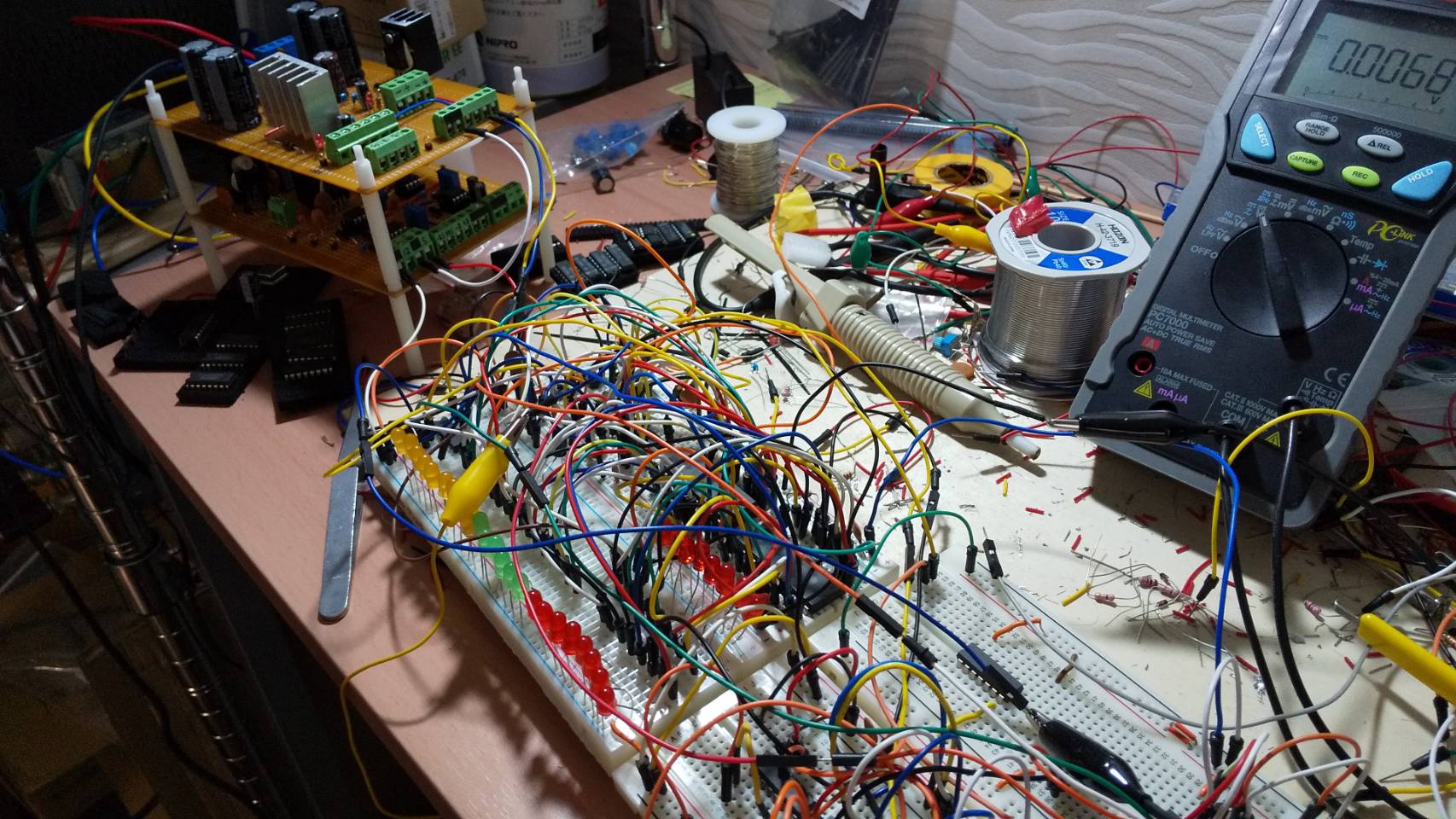

↑ 積分器+制御回路のブレッドボード上での実験の様子

続いて乗算器。欠かすことのできない基本演算要素であるが、試作機ではアナログデバイセズ社のAD633を2つ搭載していたのみで、非線形演算能力が大層貧弱であった。何しろ秋月電子でも1個2100円である。8PinDIPで2100円ですよ…。

2重振り子のシミュレーションに必要なのがちょうど乗算器16個ということなので、それを1つの目安に16個の乗算器を設置することとした。昔の商用アナログコンピュータも、乗算器が高価であるがため、なかなか数を増やすことができなかったようである。 時分割式乗算器・三角波乗算器・1/4自乗方式乗算器・サーボ掛算器などが一般的でモジュールが大型にならざるを得なかった当時と比較して、8PinDIPで比較的高精度な2変数アナログ乗算を行うICが手に入る現代はかなり恵まれているな思う。

(アナログデバイセズ社 安価な乗算器AD633)

試作機の2つの他に新たに7つ(1つは予備)を購入。残り8つはAD633ではなく、鈴商にて1500円で売っていたAD632AHZを購入して充てた。1996年製造。今やディスコンのTO-100(10PinメタルCANタイプ)パッケージである。

.jpg)

(アナログデバイセズ社 AD632)

修理時を考えるとソケットを使いたいのだが、その美しい脚をまげて14Pinのソケットに強引に挿し込むのは嫌なので、TO-100用ソケットも購入した。(何円したか忘れたが結構高価だったと思う。10PinのCAN用ソケットとか今時誰も買わんだろう)だがその肝心のソケットはそのままではユニバーサル基板に入らない。 フットプリントをダウンロードして変換基板のようなものを設計してJLCPCBに注文した。届いた基板が下の写真。

.jpg)

もっと小さく作るべきであったか…。

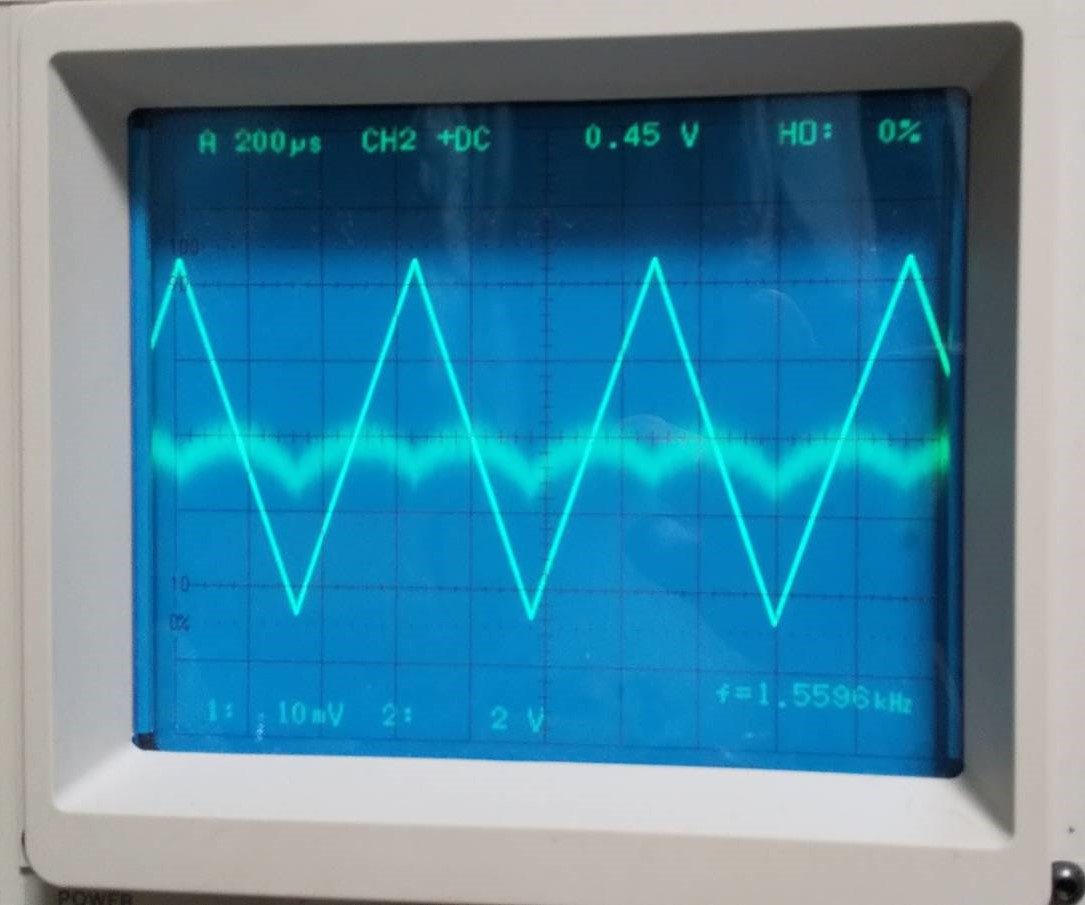

乗算器で正弦波の2乗を試してみた。\(\sin^{2}{\omega t}=1/2 (1-\cos(2\omega t))\)なる三角関数の恒等式をアナログオシロスコープで確かめることができた。

AD632用の基板も発注し、アナログコンピュータ用基板に実装するつもりであったが、フィードスルー(一方の入力端子をGNDに接続しても出力が完全に0Vにならず、GNDに接続していない方の入力電圧波形がわずかに漏れ出る現象)の如何を試験したところ、AD633のフィードスルーと比較してAD632のそれが無視できないほど大きいことが判明した。

(↑ AD632のフィードスルー 一方の入力端子を0Vに固定してもう一方に三角波を与えている。0に何を乗じても0二しかならないのだから理想的には出力は完全な0Vになるはずだが、実際にはご覧の通りリークが生じる。これがフィードスルー誤差である。このAD632の場合10mV程度の誤差が発生しているようだ。)

AD633は安価なだけあって公称誤差がフルスケールの2%もあるが、実際のオフセット・フィードスルーはデータシート上のスペックよりかなり良く、オフセット電圧に至っては1mVもない(データシートでの保障値は30mVである)。いっぽうAD632(メタルキャンタイプ)はオフセット・フィードスルー誤差が大きく、トリム回路が必要と思われる。

以上の事情からAD632の使用は不都合であると判断し、超高価で高精度な乗除算器「AD734」をAD632の代わりに使うことにした。せっかくAD632用の基板も作ったのにもったいないが…。

(↑ AD734)

(↑ AD734)

AD734は既にオークションで廉価にて大量落札しており、手元に十分なストックがある。(Digikeyで買えば単価1万円はくだらないが数百円で落札できた。)AD734はフルスケール0.1%とかなりの高精度を誇るが、特性にかなりばらつきがあったため、オフセットが規定値以内の個体を10個ほど厳選した。 電源投入後5~10分ほど待たないとオフセット電圧が安定しないので注意が必要である。手でパッケージを触るとほんのりと感じることができるくらい温まる。

演算基準電圧(±10V,±1V)は、高精度リファレンスの出力(+10V)を低オフセット高精度オペアンプの反転増幅回路と組み合わせることで次々と生成する方式である。当初はLM4040(TO-92パッケージで精度0.1%のシャントレギュレータ。単価289円)を使用するつもりであったが、コンピュータで行われる演算のすべての基準となる部分であるだけに、もう一桁くらい精度が上のICを使ったほうがよいだろうと判断し、LT1236ACN8-10(精度0.05%)に変更した。単価1300円程度である。私の財政的にこのくらいの価格が限界であった。誤差0.05%とあるが、トリムポテンショメータを接続してオフセットを調節するための端子を有しており、10.000V程度の精度に調整可能である。ドリフトも2ppm/℃とほどほどに小さい。

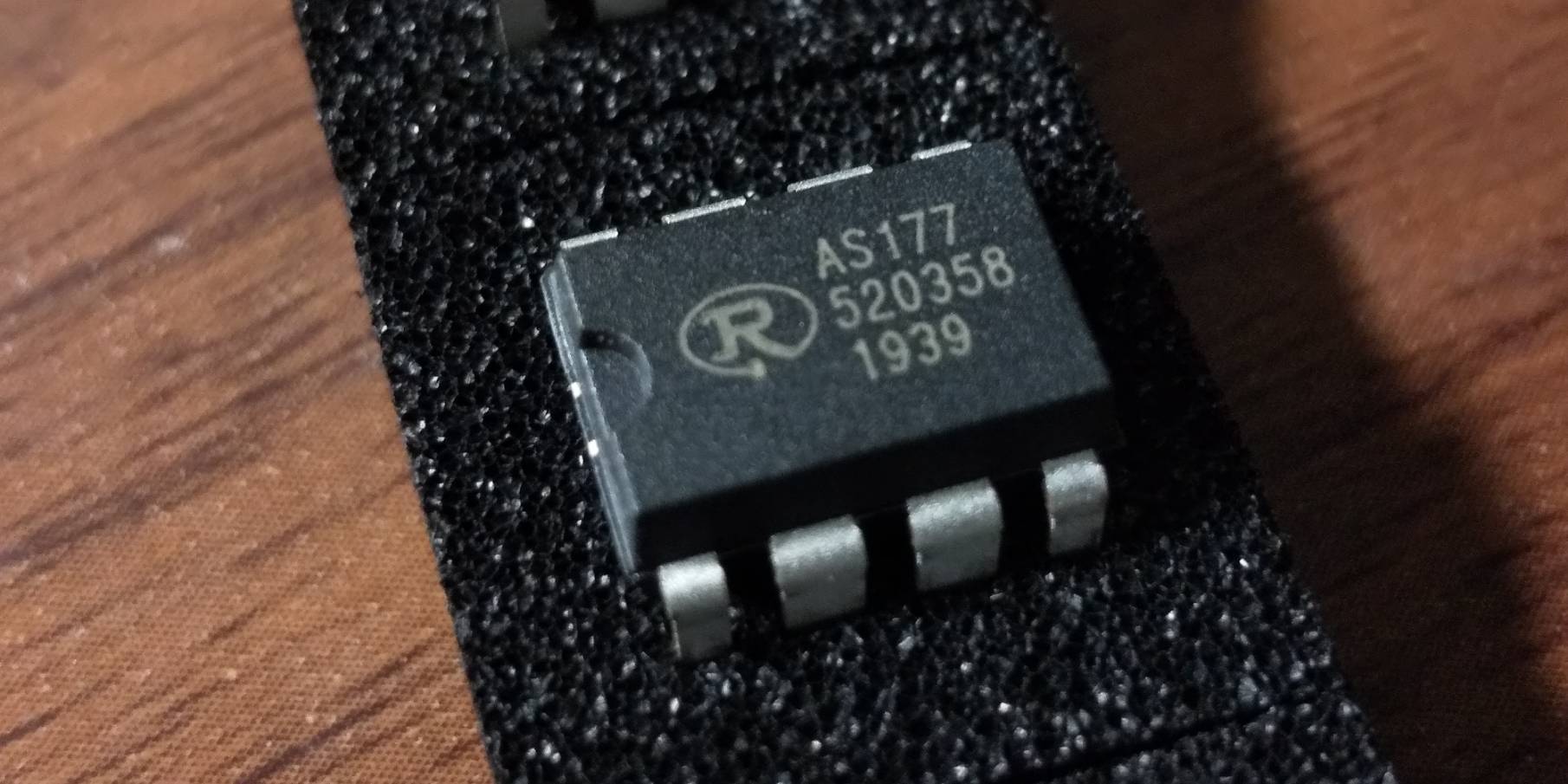

演算電圧を生成するオペアンプは、当初OP07を用いるはずだったが、後にAS177に変更した。

OP177の安価なセカンドソース品である。オフセット電圧は25℃で±40µV max。オフセットドリフトは±0.8μV/℃ avg。十分優秀である。

この自作アナログコンピュータの演算部では各部回路切り替え部にリレーの代わりにアナログスイッチを使っており、高速動作を可能にしている。当然ながら、少なくとも±10Vの正負信号を扱えるICでなくてはならない。オン抵抗は演算精度に影響するので低い方がよいのだが、各演算器の入出力インピーダンスについて細心の注意を払って設計しているので、演算回路中に流れる電流はμAのオーダーに抑えられるからあまり気にしなくてもよい(と思う)。

2. 設計・製作

紆余曲折あり何度も設計を見直す羽目になった。いろいろ改廃した結果、最終設計案がまとまったのは大学の夏休み期間中(8月ごろ)。実家に帰省している間のことであった。帰省から帰ったのち半田ごてを使ってユニバーサル基板上に回路を仕上げることになる。当初は夏休み中に完成するつもりで計画を立てていたが、諸事情あって大幅に遅延した次第。

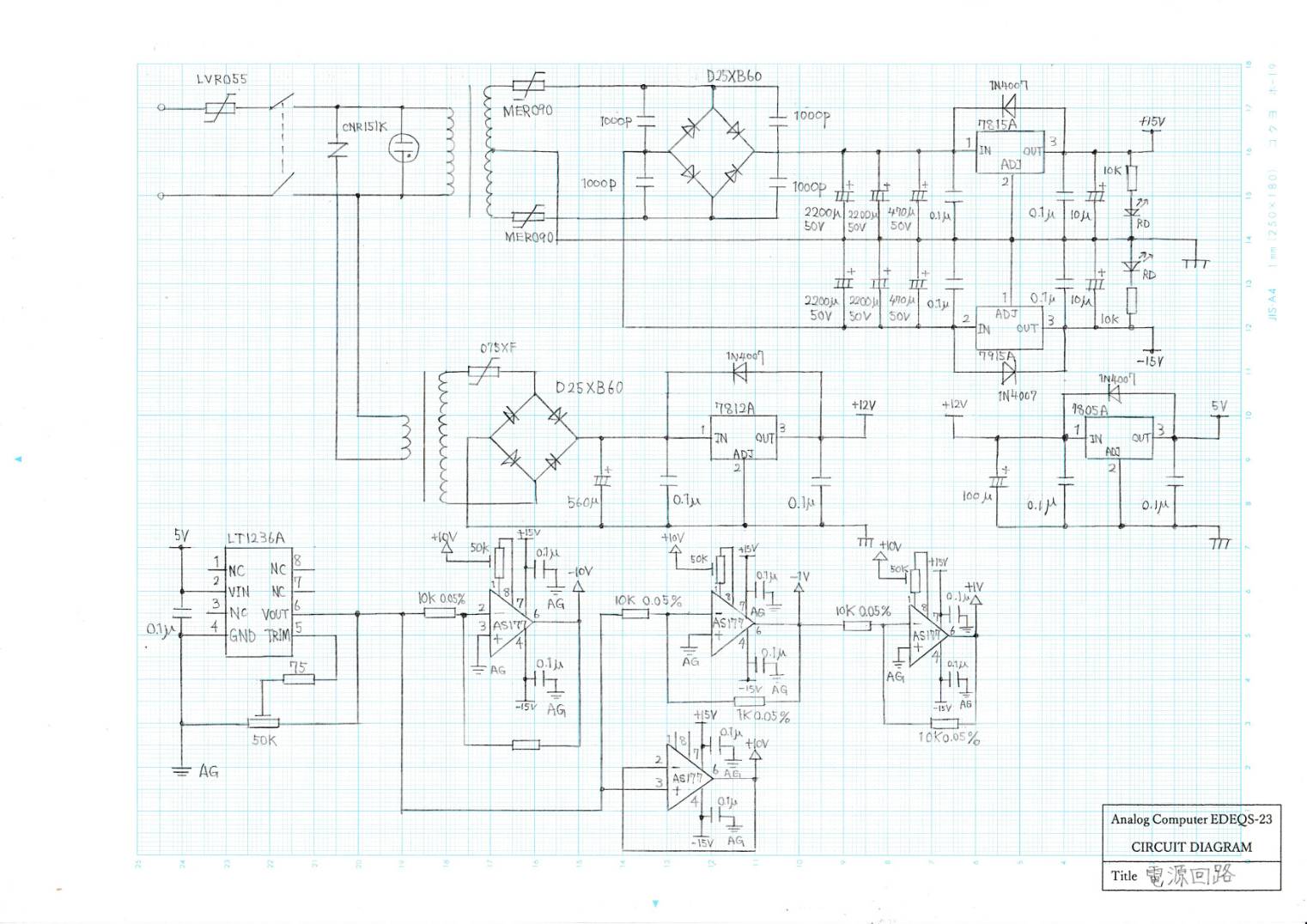

2.1 電源回路及び基準電圧回路

電源回路(上)と基準電圧回路(下)の回路図

電源は三端子レギュレータを用いた定電圧回路で正負電圧(±15V)を供給しているほか、リレー用12V、ロジック用5Vも生成している。特に語ることは無い。演算基準電圧は前述の高精度電圧リファレンスLT1236から供給される+10V(0.05%)をオペアンプで反転・増減して-10Vや±1Vを生成し、前面パネルに提供する。そのオペアンプはAS177を用いている。その際、反転増幅器の抵抗には誤差0.05%、温度係数±25ppm/℃の高精度金属皮膜抵抗を使った。

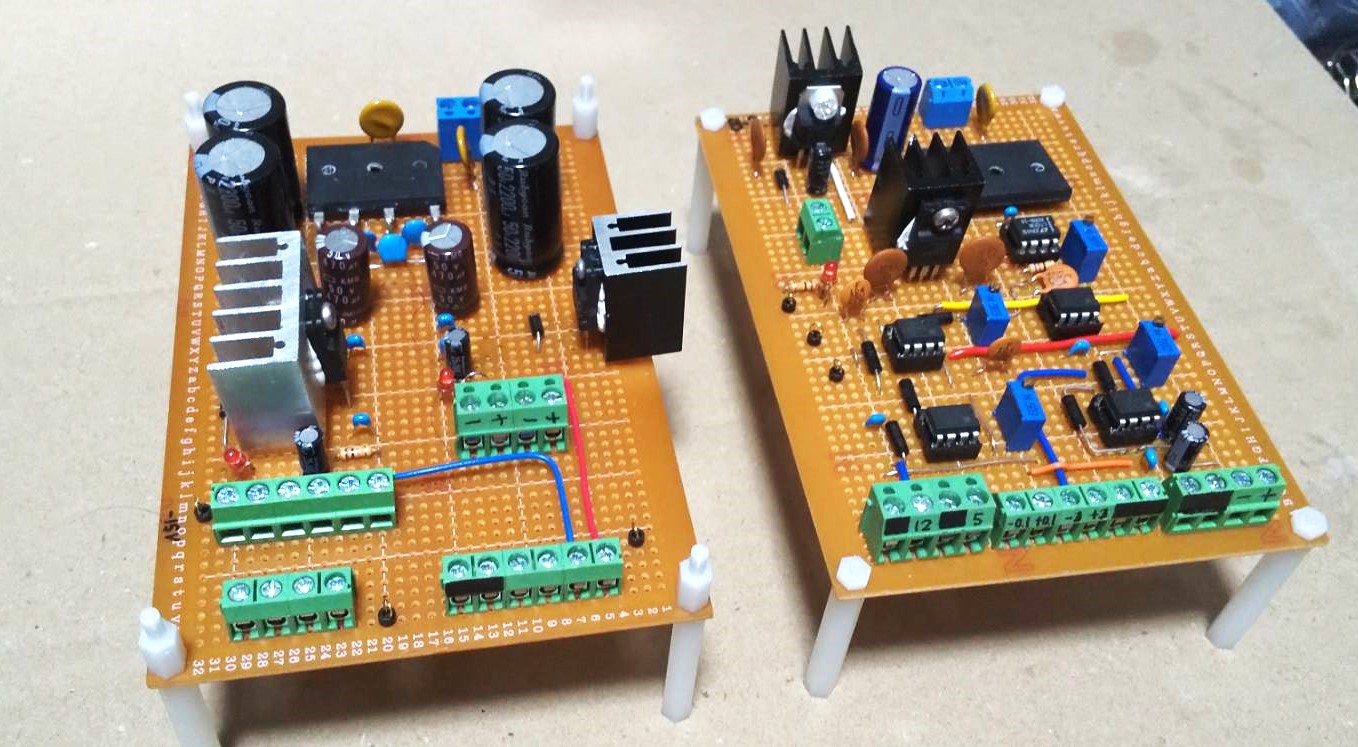

完成した電源回路・基準電圧回路の基板がこちら (↓)。サンハヤトのユニバーサル基板ICB-505を用いて製作した。

右の方が基準電圧基板。

右の方が基準電圧基板。

.jpg)

稼働状態で長時間放置して基準電圧のドリフトを調べたが、電圧値はほとんど変わらず、予想以上の安定性を示した。

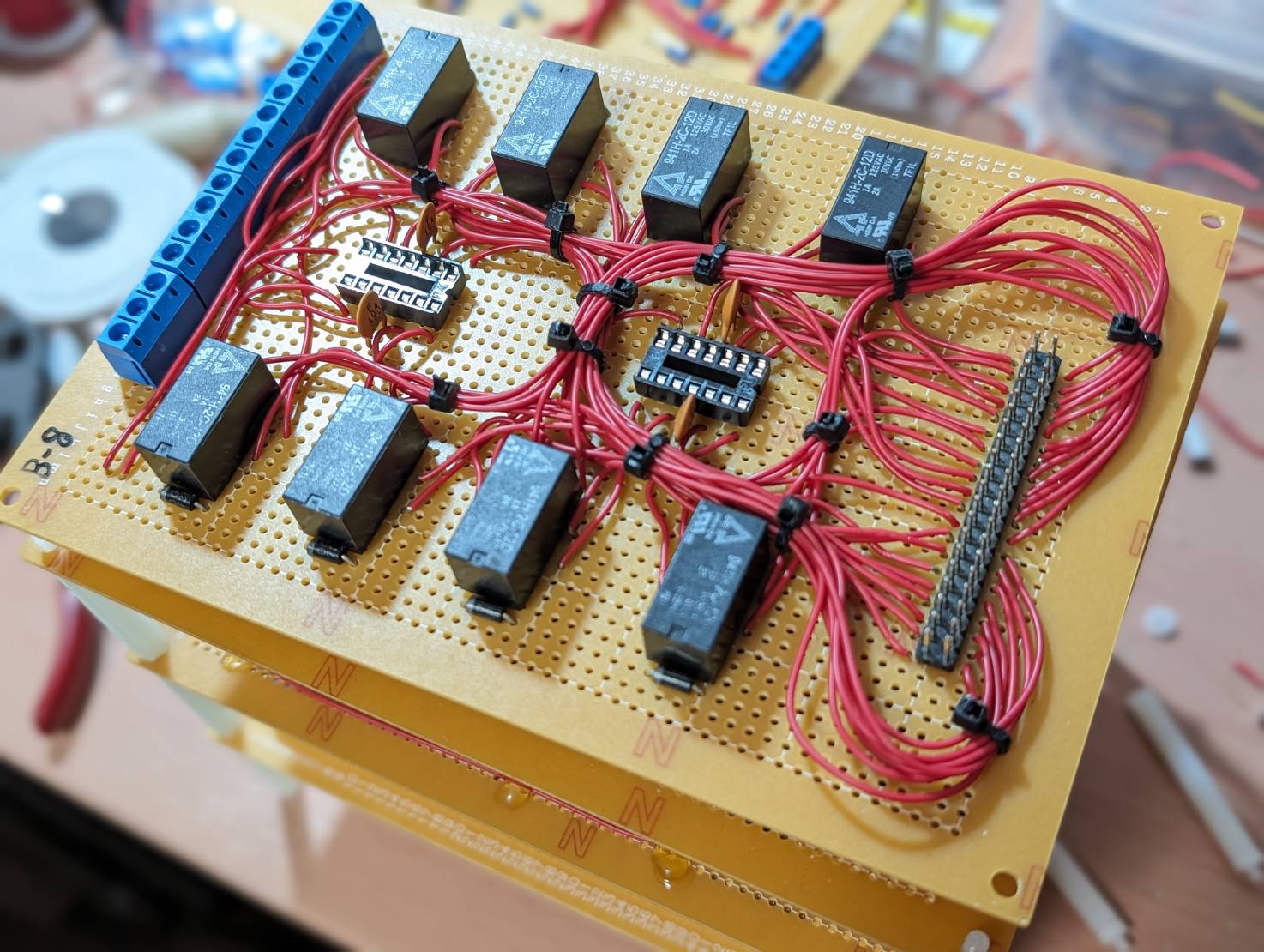

2.2 制御回路類

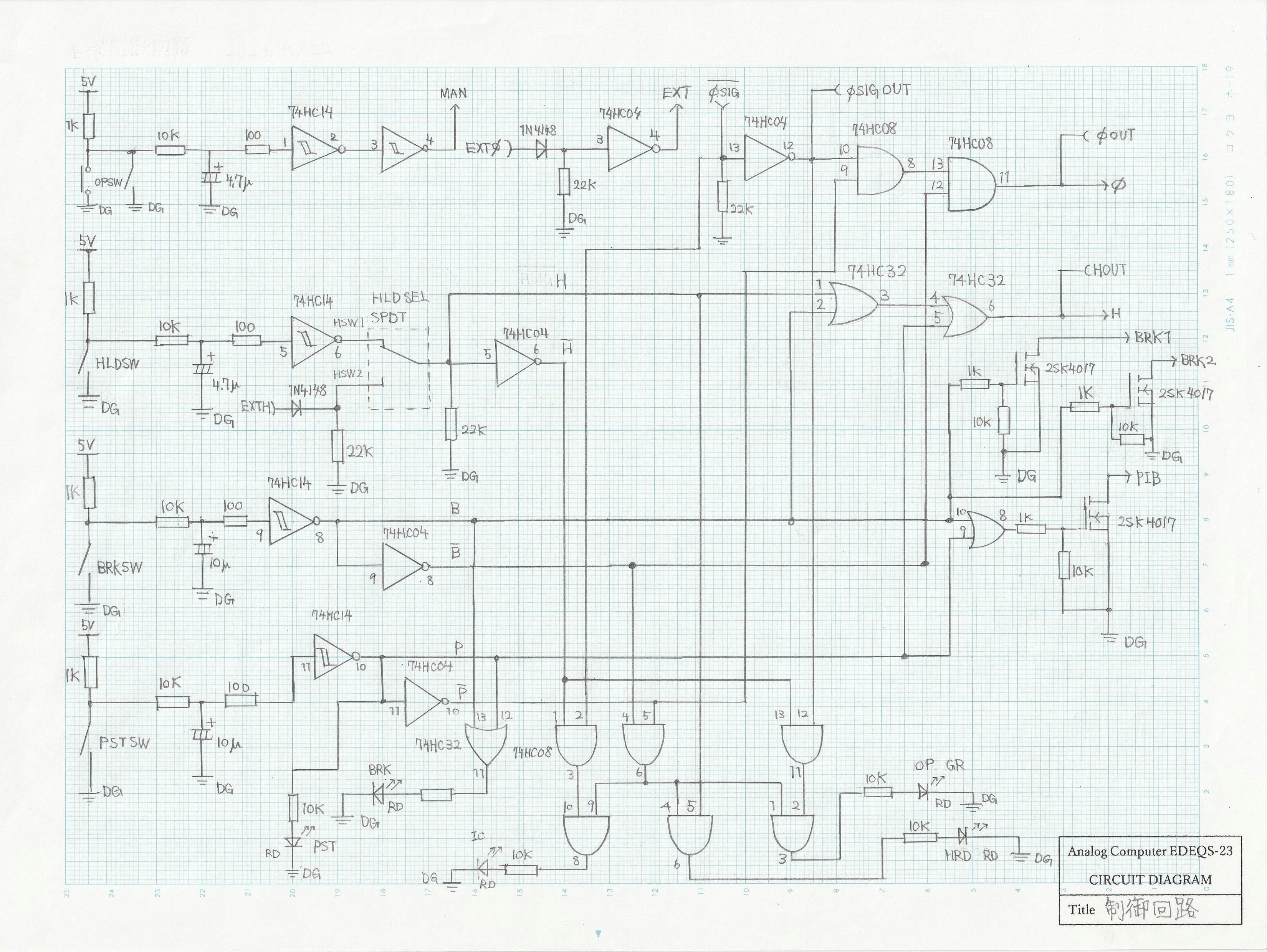

下は演算モード(初期条件・演算・保持など)の制御回路の回路図。

各モードの略称:OPが「演算」ICが「初期条件」HLDが「保持」PST(PotSet)が「係数設定」BRK(Break)が「開路」

演算、初期条件、保持については「演算の理論」のページで説明しているのでここでは言及しない。

PSTは係数器の値を設定するモード。具体的には、すべての係数器(通常の係数器16個+非接地係数器2個)の入力端子がリレーの駆動によりパッチパネルのバナナソケット部から内部の高精度基準電圧源「1V」に切り替わり、出力も同様にパッチパネルの各係数器出力端子ソケットから(POTセレクタを通して)POTSET専用出力ポートに切り替わる。セレクタ(ロータリースイッチ)で係数器を選択すると、当該係数器の設定値が電圧として専用出力ポートに出力されるため、そこで電圧を計測しながらポテンショメータのツマミを回して精密な係数値を設定できる仕組みである。このPOTSETモード時には積分器・加算器・乗算器の出力もリレーで演算回路から切り離され、さらに係数ポテンショメーターの入力に自動的に「1V」が加えられるため、わざわざパッチコード(バナナプラグ)を外して係数器の入力に1Vを加える手間が不要であり、演算回路そのままで係数設定の作業が可能になる。

BREAK(開路)モードも設定した。文字通り、積分器・加算器・乗算器・係数器・演算基準電圧源の出力をリレーを用いてパネル上ソケットから切り離し、演算回路を開く。出力がGNDへ直結されるなどのパッチエラー・異常がある場合、直ちにBRKボタンを押して演算回路を開き、プログラムをチェックしなくてはならない。(当初の計画では、電流の異常、演算器の出力電圧飽和を検知すると自動でBRKがHighになる回路を考えていたが、断念した。かつての商用アナログコンピュータのように係数ポテンショメータの入力にヒューズを入れることも考えていたがこちらも断念。)

BRKやPSTでは、12VリレーをMOSFET(2SK4017)で駆動する。各モード設定は押しボタンスイッチで行い、モードの状態はフロントパネルのLEDで表示する。

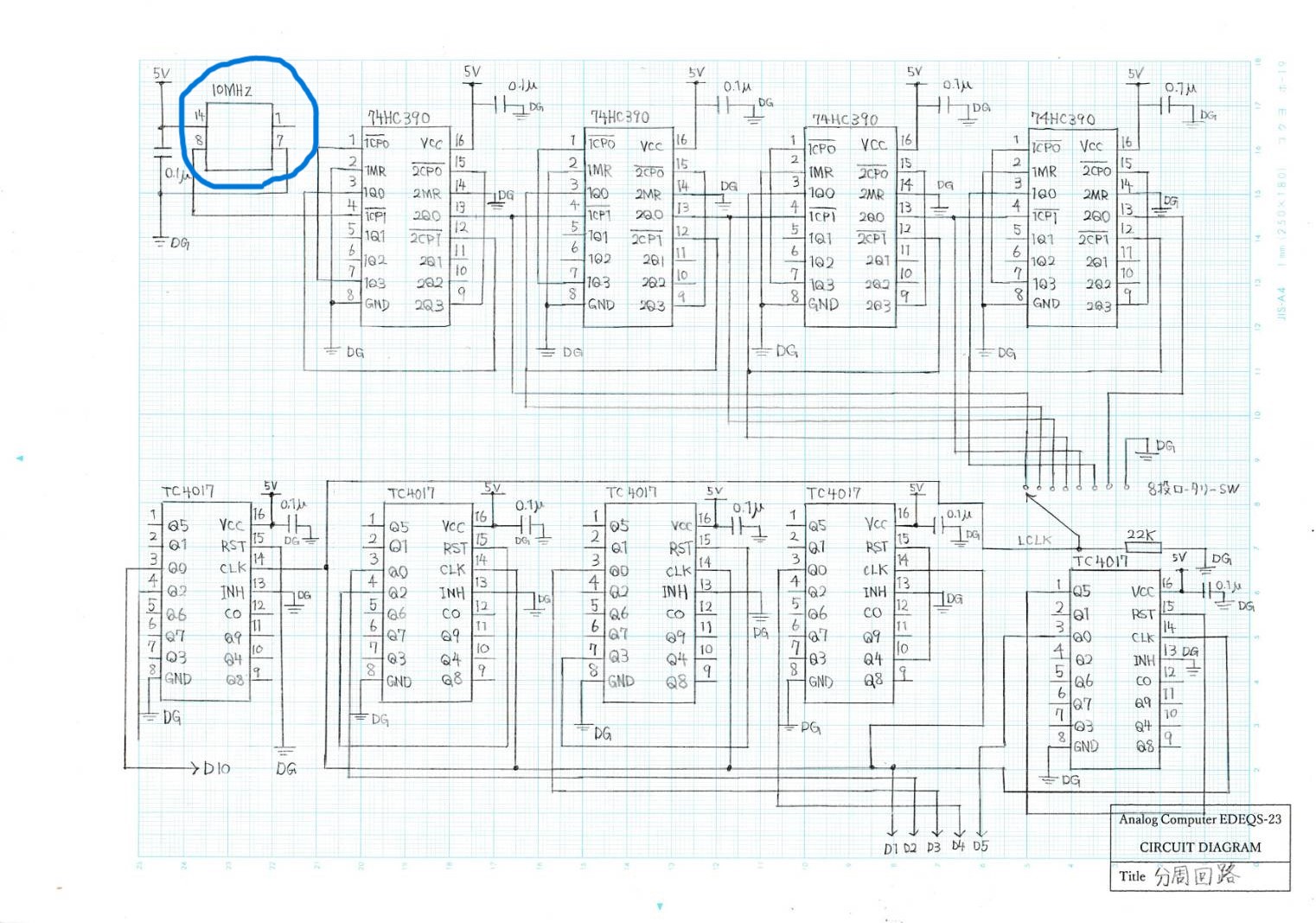

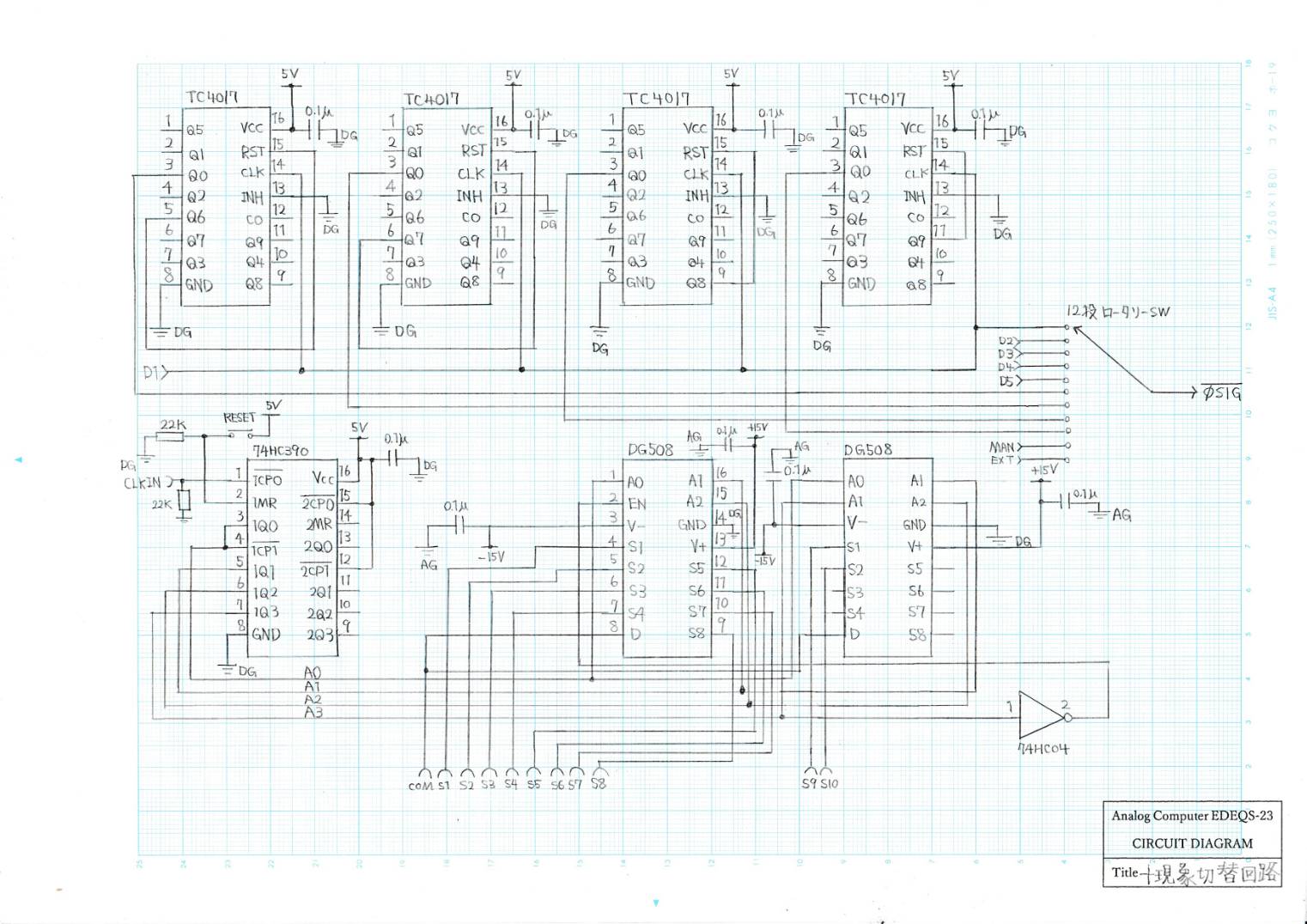

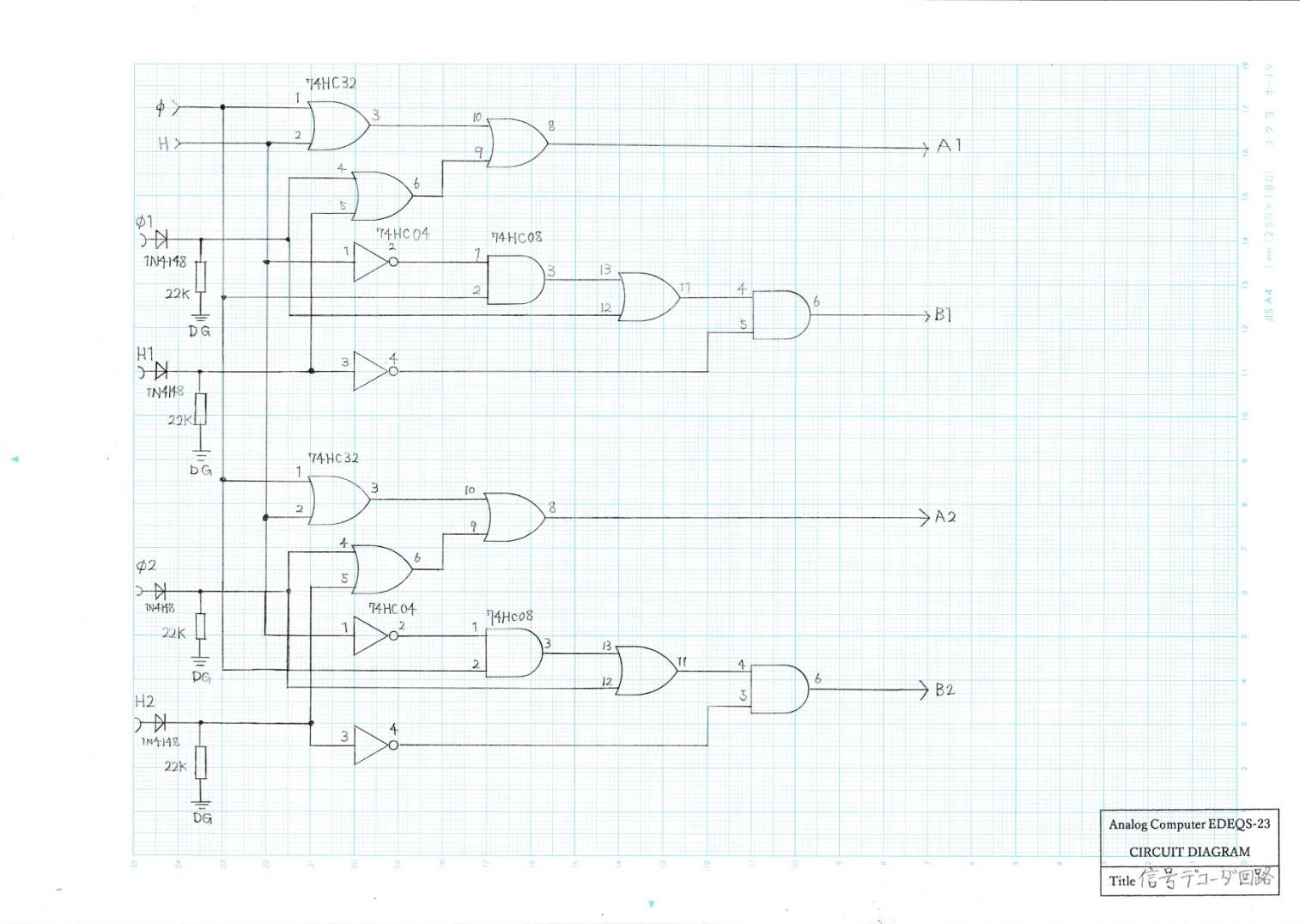

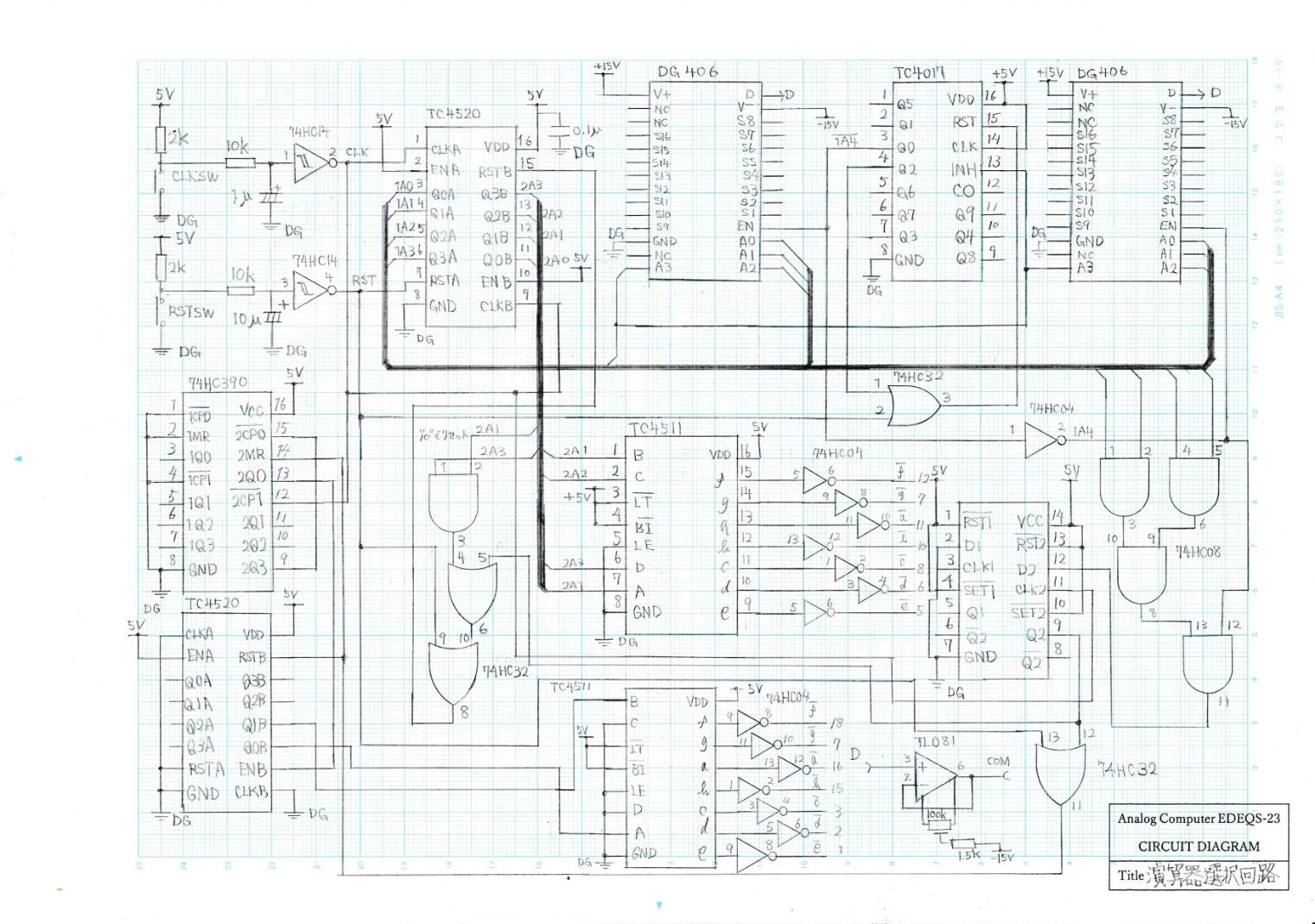

次に、分周回路及び同期式十現象切替器の回路図。

(訂正:74HC390の14ピン「2MR」は回路図では何処にも繋がっていませんが、正しくはGNDに接続します。)

10MHz発振器のクロック信号を74HC390や4017で分周を繰り返し、\(n\times10^{k}\) [Hz]の任意ロジック信号「\(\phi\)」を生成できるようにする(ただし0.1Hz~100kの範囲)。この信号は、高速繰り返し動作で積分器の「演算⇔初期条件」の切り替えを行うためのクロックであり、積分周期を決定する。整数\(n,k \)はフロントパネルのロータリースイッチで設定する。このほかHOLD信号(\(H\))は手動スイッチ、もしくは外部からのロジックで制御され、HOLD信号がHighになると全積分器の状態が\(\phi\)の値に依らず「保持」となる。\(H\)信号と\(\phi\)信号は積分信号デコードロジックでデコードされ、積分器のアナログスイッチを駆動する。積分器以外に比較器も\(\phi\)信号と同期する。(\(\phi\)=0Vすなわち演算状態でない場合の比較器のロジック出力を入力電圧にかかわらず0Vにするため。)

回路図2枚目の下半分は同期式十現象切替器である。外部から入力された信号(\(\phi\)信号やそれを分周した信号など、5Vロジックレベルなら何でもよい)に同期して、アナログスイッチ(10way)を順次選択する回路である。SP8Tのアナログスイッチ(DG508)を2つ使っている。この回路を(積分\(\phi\)信号周期の整数倍の周期を持つ)クロックで駆動すると、式のパラメータを演算実行中に離散的に変化させた時の複数の解をアナログオシロの画面上で同時に観察できる。この動作を「反復演算(iterative operation)」もしくは「自動設定繰り返し演算(automatic sequential operation)」という(JIS規格により定義された語である)。

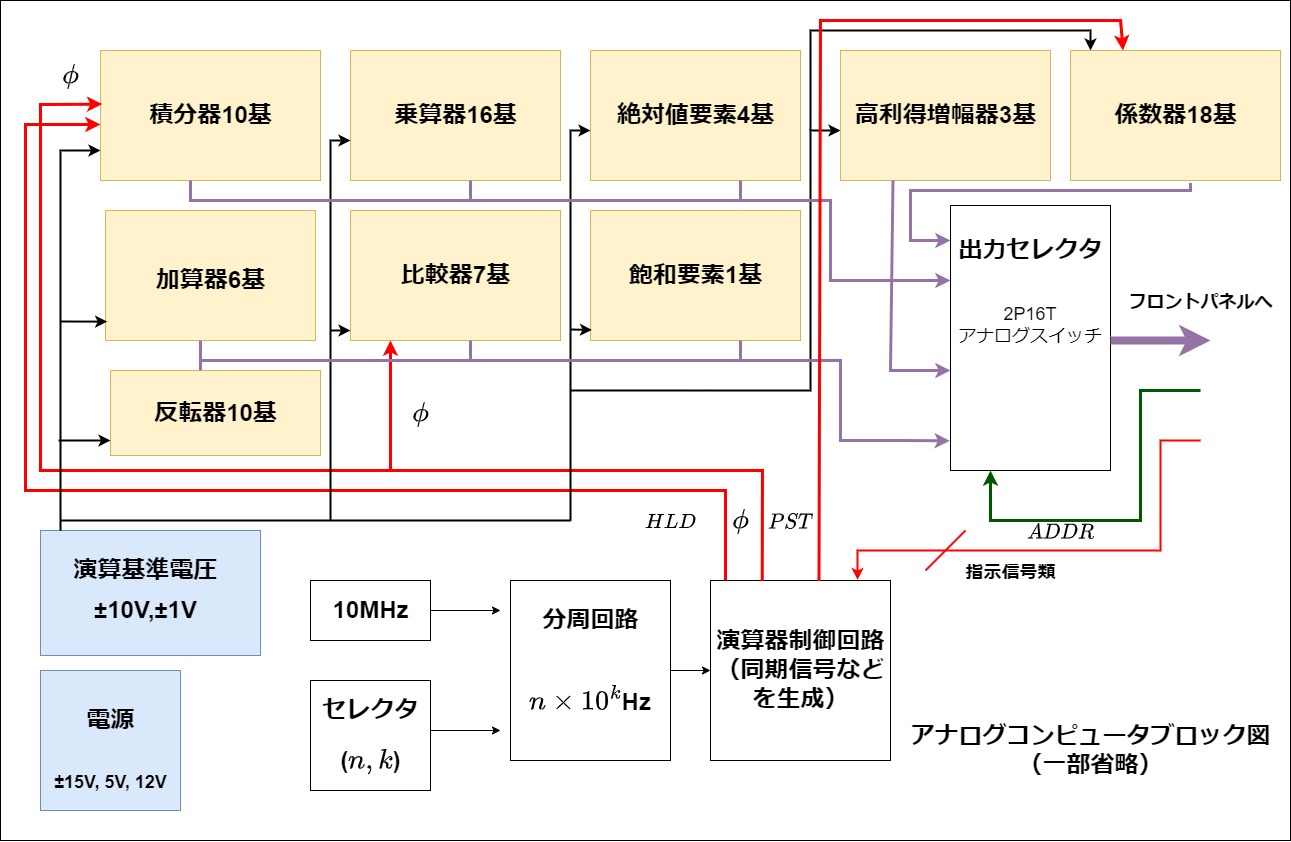

自作アナログコンピュータの大まかなブロック図 (↓)

制御回路からの信号がアナログコンピュータ全体を統制している。しかし、絶対値要素や反転器など、制御回路の統制の外に置かれている演算器もある。これらは(計算機の電源が入っている限り)現在のモードに依らず入力に対し常に演算結果を出力する。

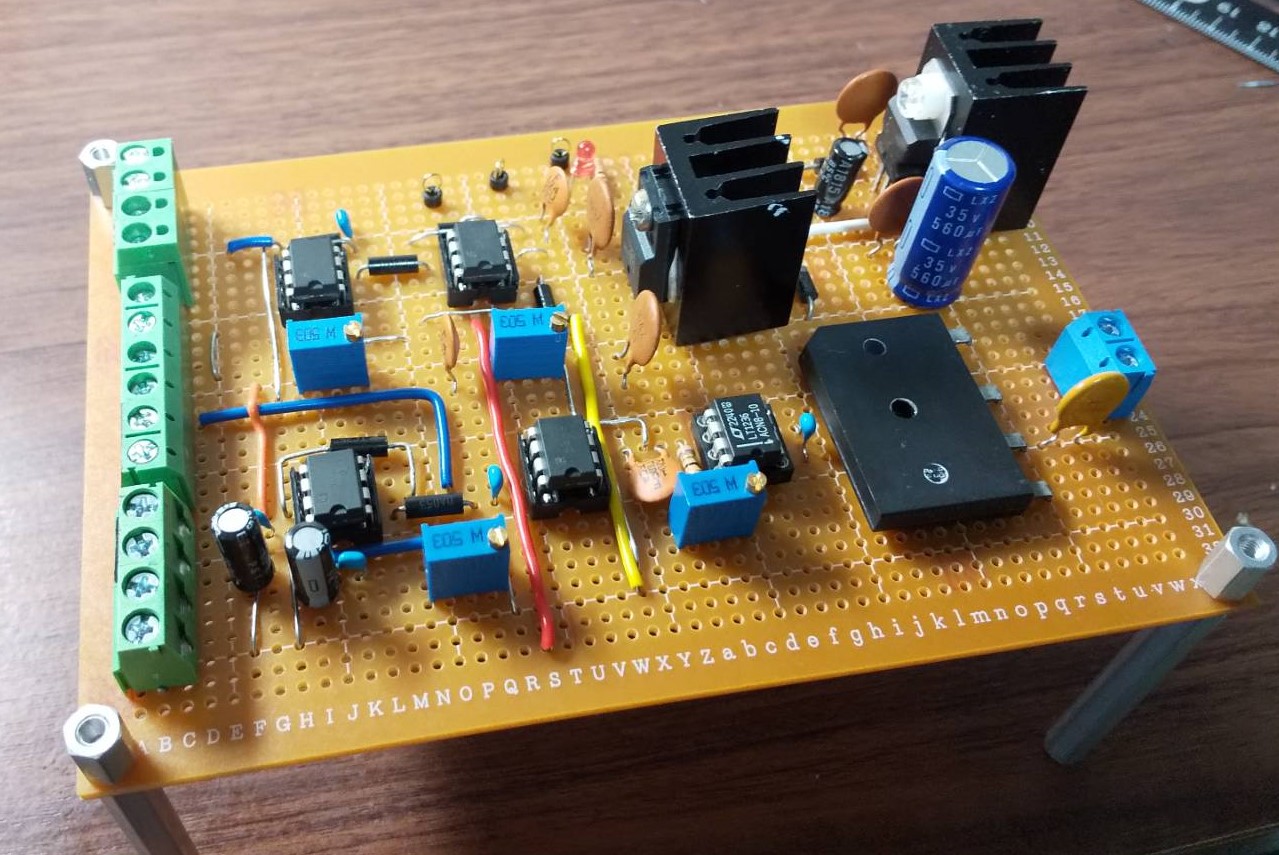

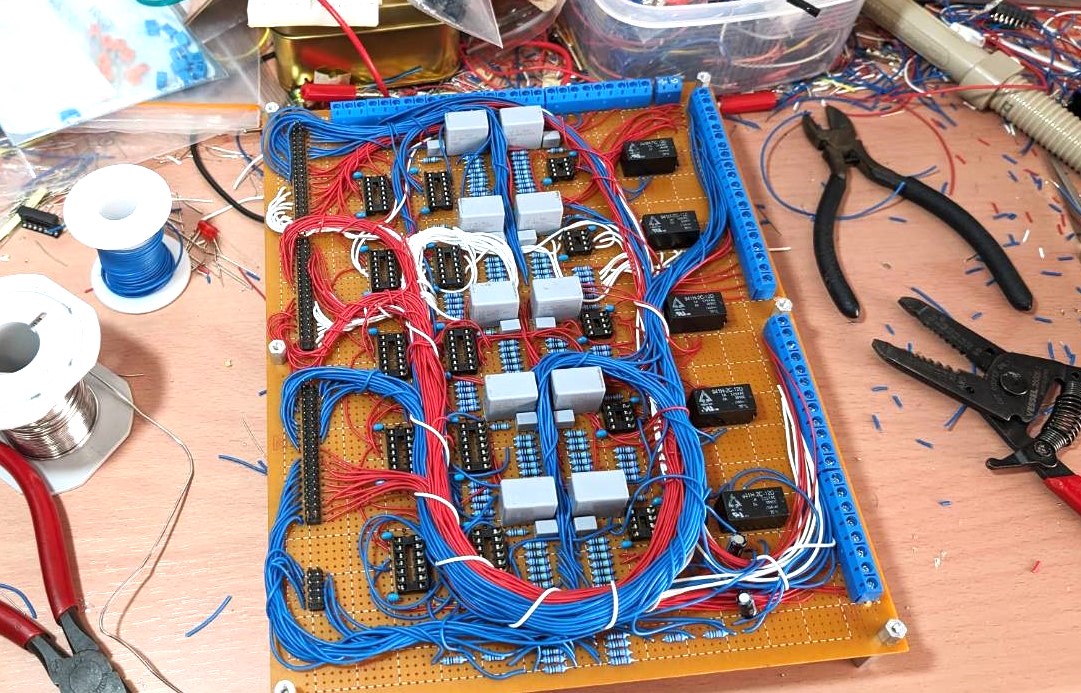

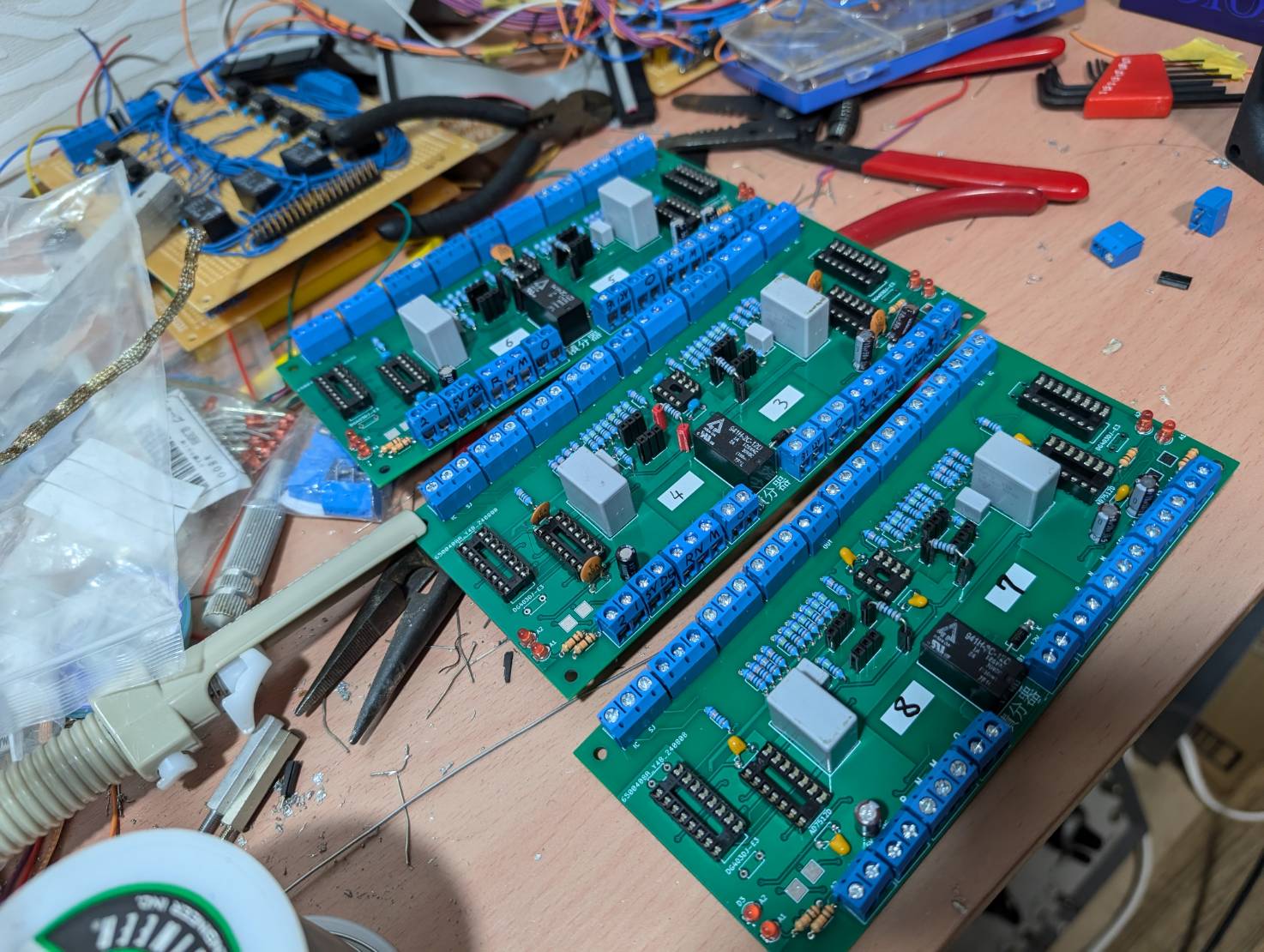

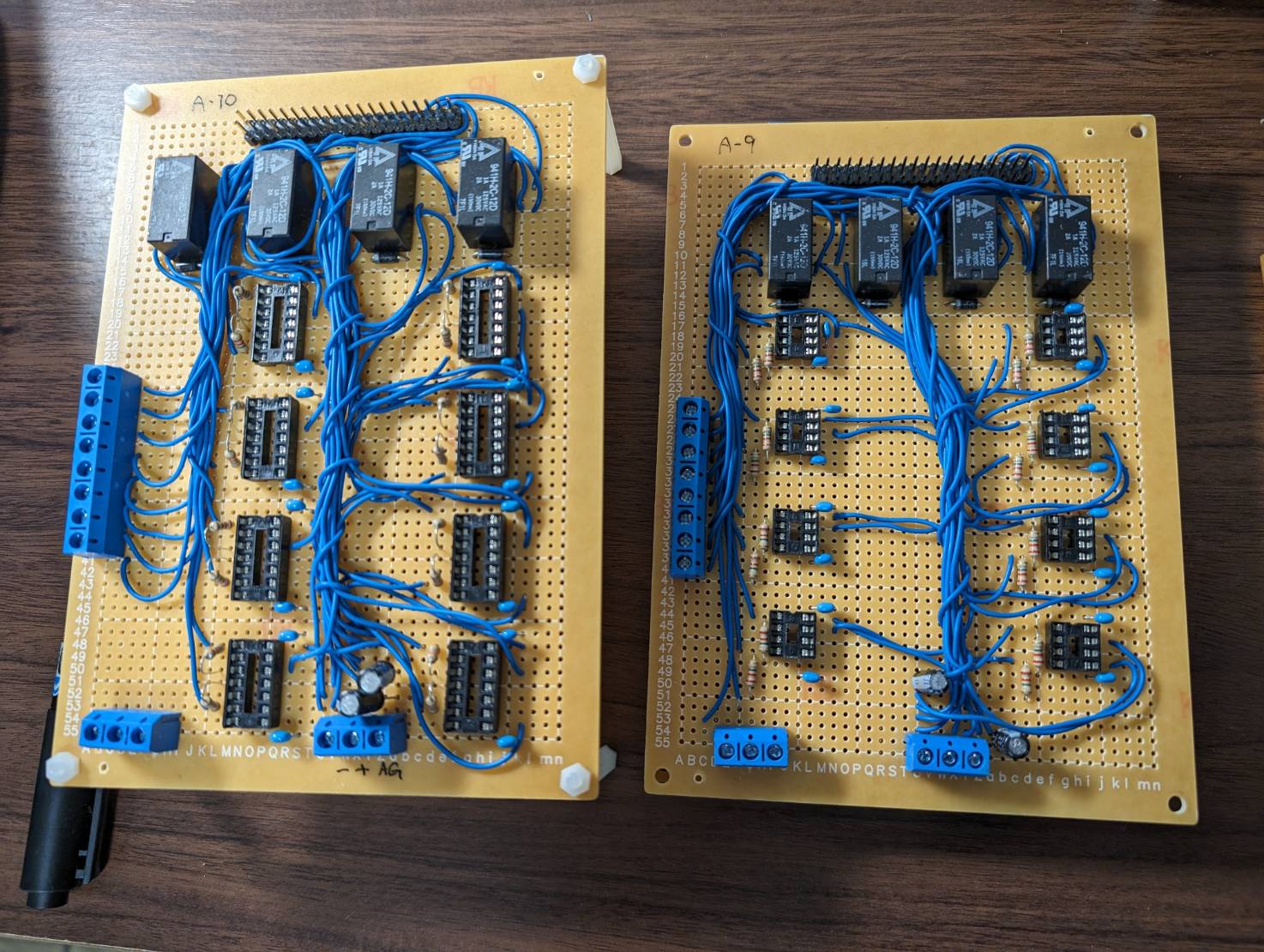

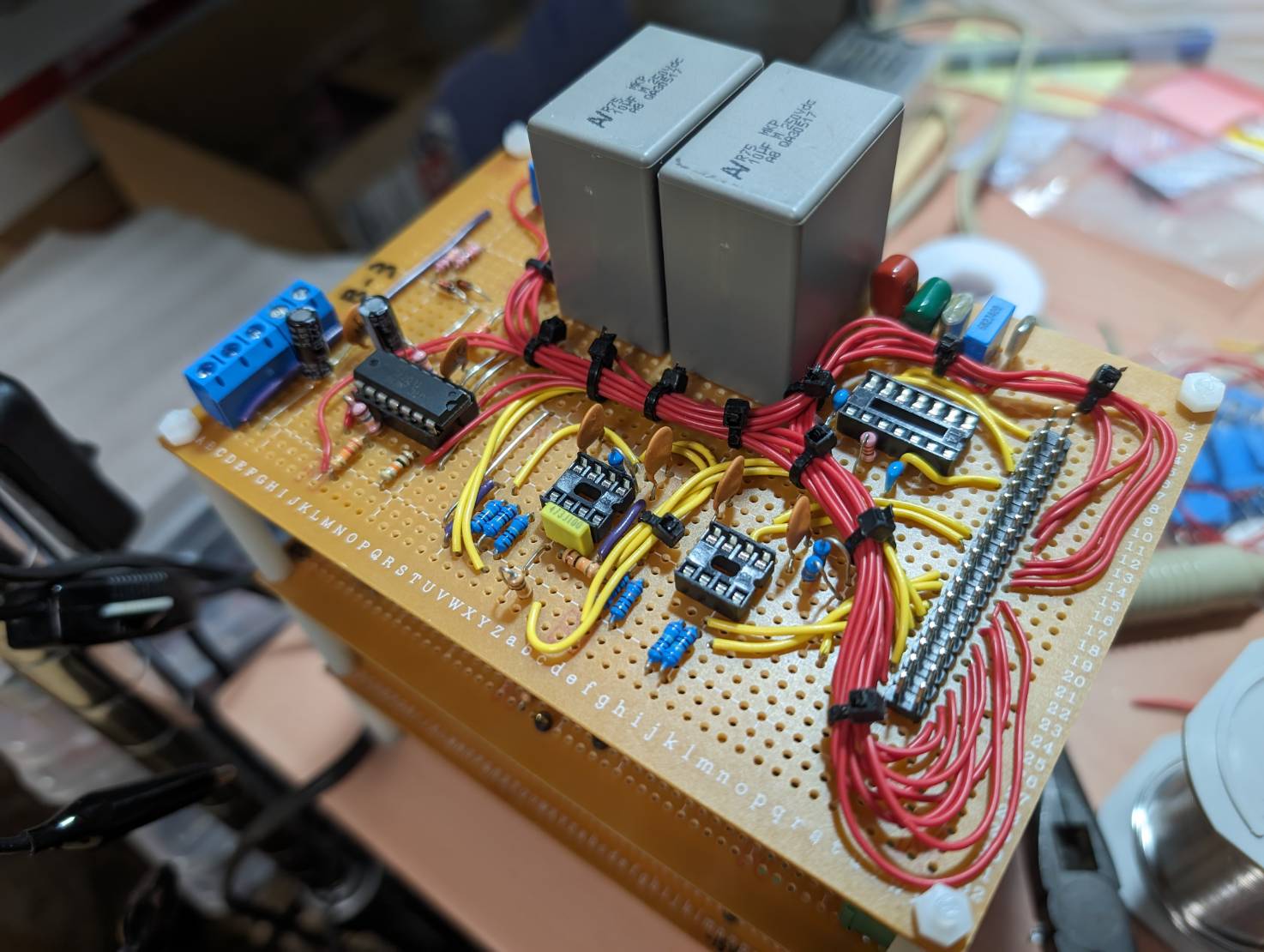

制御関係の基板の写真↓

2.3 積分器/加算器/反転器

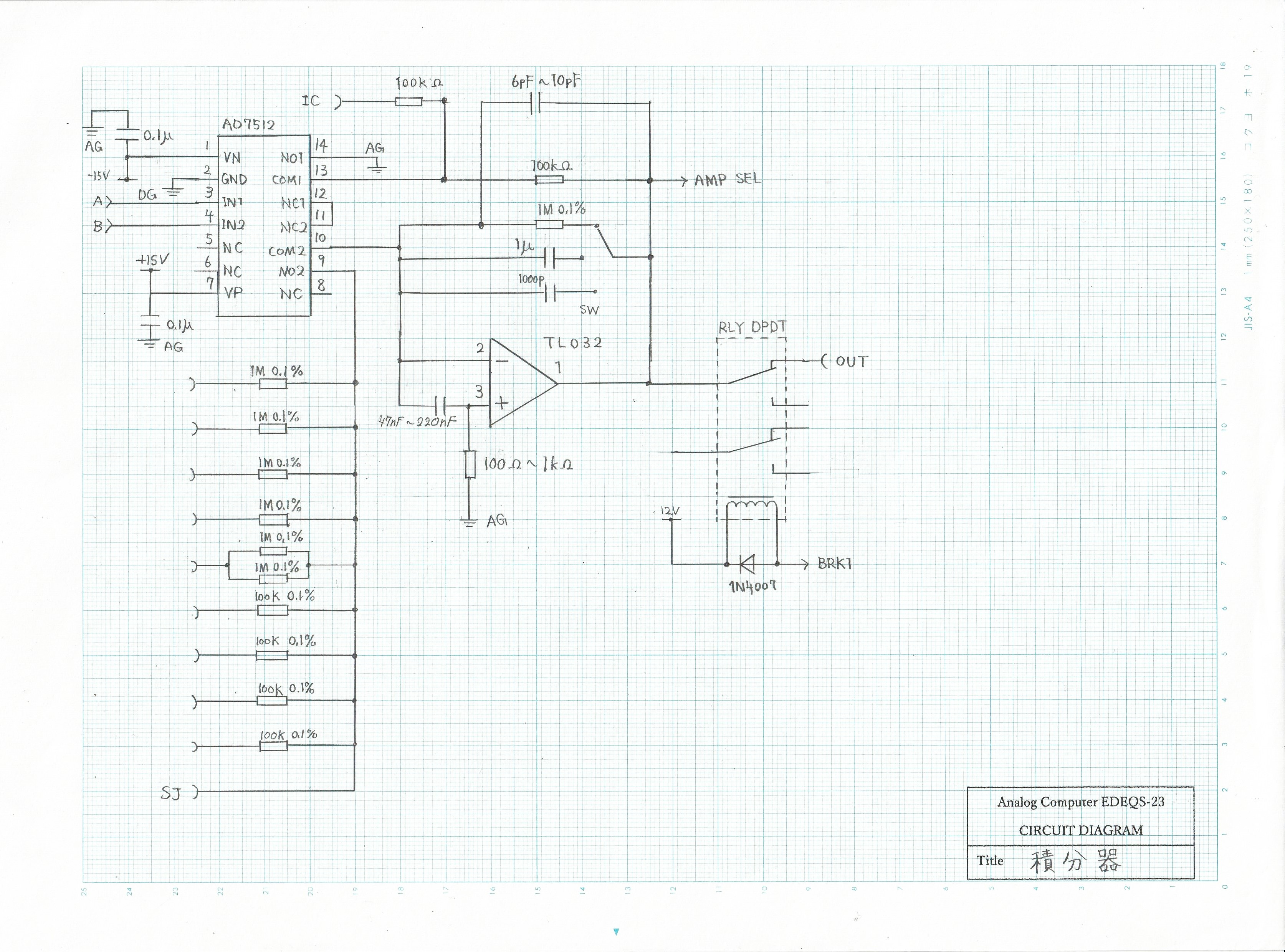

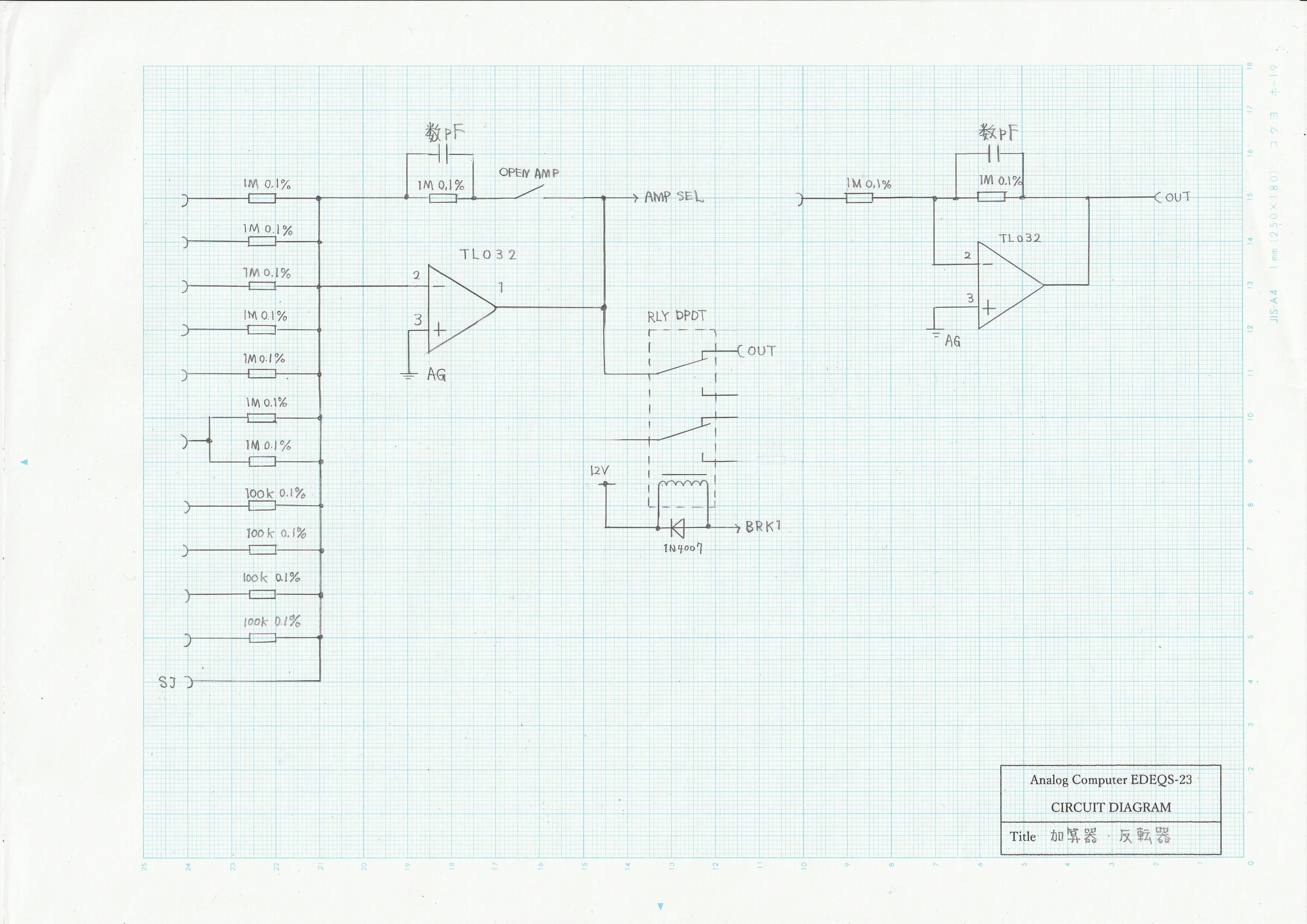

下は積分器・加算器・反転器の回路図。

↑ 積分器

↑加算器・反転器

積分器と加算器の出力はBRK信号がHighになるとリレーでパッチパネルから切り離される。積分器は10個、加算器は6個、反転器は10個必要になる。積分器の動作については「演算の理論 積分器」に詳しく書いたのでそちらを見て頂きたい。上の回路図では、加算器や反転器のフィードバックに入力浮遊容量を補償するための小容量コンデンサが挿入されているが、実際は周波数特性を実験で確認して、高周波で位相が進むようであれば入力部の抵抗の方にコンデンサを挿入することになる(下図)。

下の回路図は積分器のアナログスイッチのデコード回路である。\(\phi\)信号や\(H\)信号の値から、アナログスイッチ(AD7512)に入力するロジックを決定する。

\(\phi\)や\(H\)信号は10個ある積分器すべてを同時に統御するための信号であるが、積分器毎に用意してある\(EXT\phi\)や\(EXTH\)入力端子を使えば積分器を個別に制御できるようになっている。これらEXT信号(個別制御信号)は常に全体制御信号(\(\phi\)や\(H\))に優先するので、ある条件が成り立った時に特定の積分器のみ保持(HOLD)状態にしてその積分器を記憶要素の代わりとして機能させることも可能。その場合は後述する比較器などの条件判断結果出力(ロジック信号)をEXT端子に入力することが多い。HOLD機能とこれらEXT端子は上手く使えば複雑な関数も実装できるのでなかなか便利だと思う。

回路図右のデコード出力信号A,Bはアナログスイッチのロジック入力。上図で積分器2個分の回路なので、これを5セット製作しなくてはならない…。

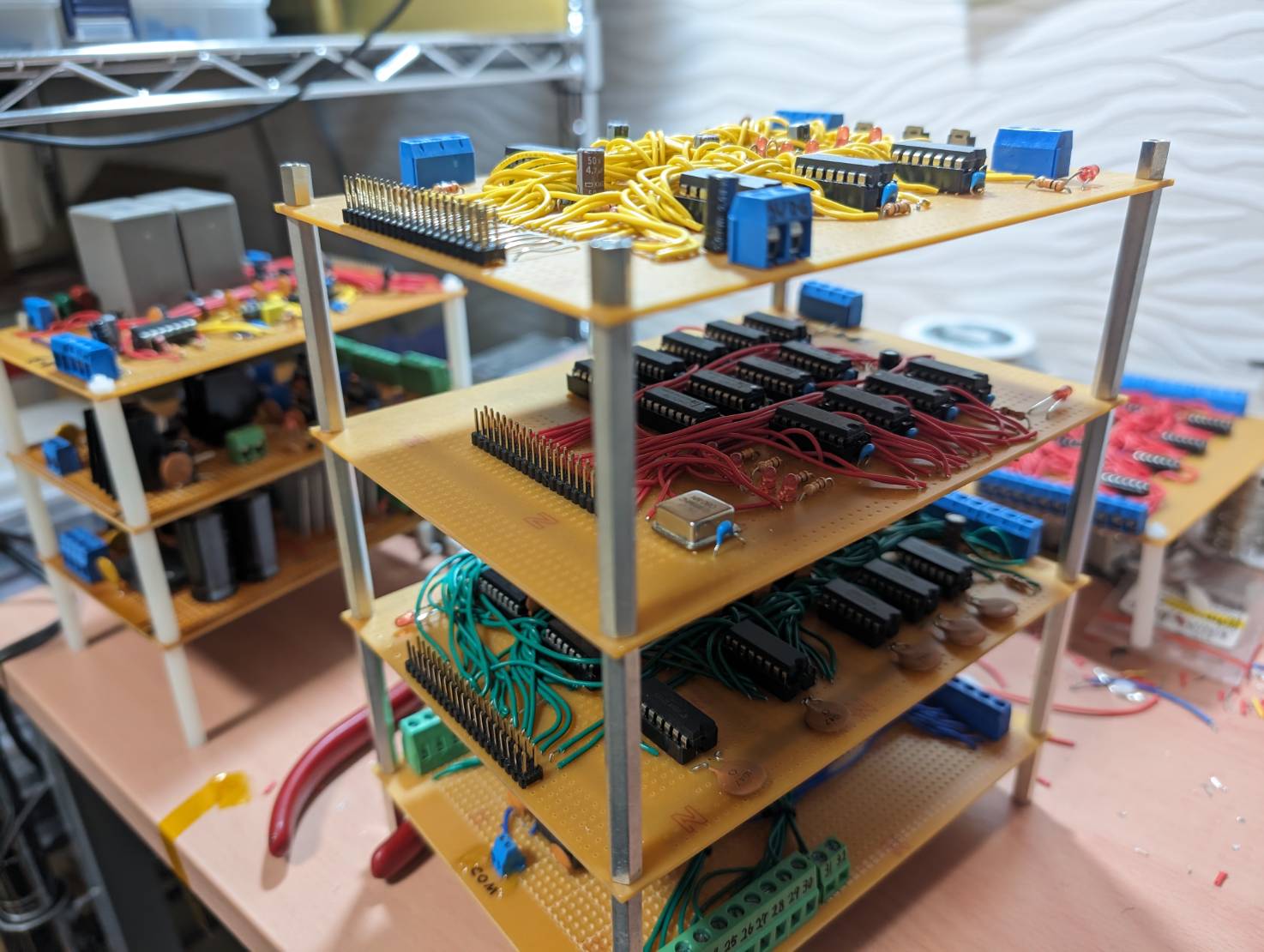

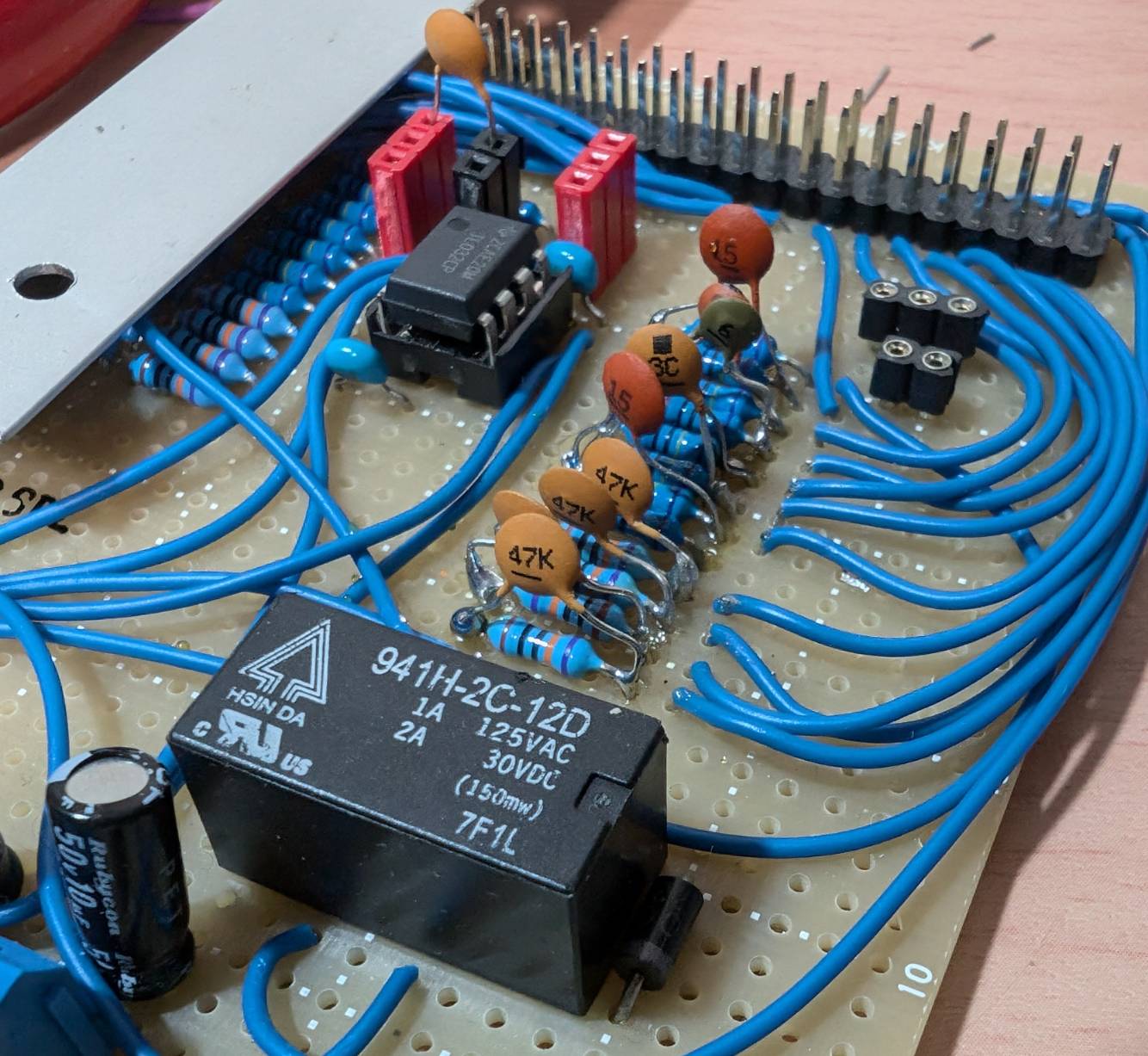

下は積分器基板の写真。見てお判りいただけると思うが配線作業がえらい大変である。私ははんだ面にビニル被膜線を這わせるのに抵抗を感じる性分なので、いつも配線は表面で行っている。ピンセットなどを駆使して家庭科の裁縫作業のごとく配線を別の配線の間に通してはまとめて束ねていく。

↓積分器基板

この積分器基板と加算器のみの演算テストを行ったところ、不具合が確認された。具体的には、サークルテストを高速モードで行い正弦曲線の減衰を調べ演算誤差を評価した結果、使い物にならないほど振幅減衰が激しいことが判明。他のブロックダイヤグラムを試しても、pythonで計算した出力と異なる解曲線だったりと、当初予想したほどの精度が出ていない。

どうやら補償用CRフィルタのみでは積分器入力部の浮遊容量は低減できないようである。さらに、積分器入力と出力の配線間での容量結合で線形減衰項が生じ、周波数特性が積分器ではなく1次遅れになっていることが分かった(無論実際にはもっと複雑に結合していると思われる)。

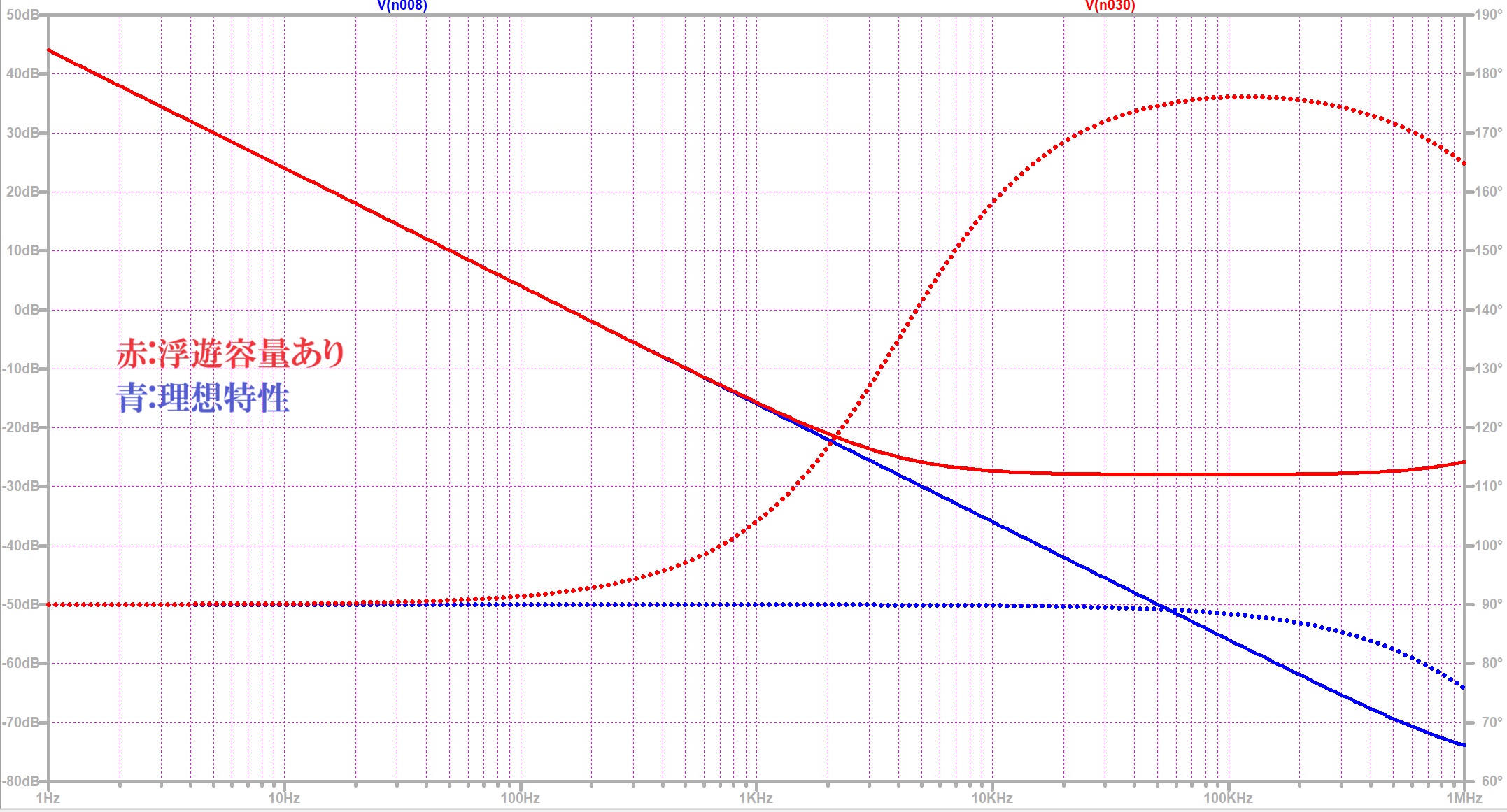

下図は浮遊容量を想定した積分器の周波数特性である。

入力・出力間の容量結合と入力L部の浮遊容量を加味した場合の微分方程式 y"+ y =0 (赤)および y' + y = 0 (青) の解波形のシミュレーション結果を下に示す。

振動解は減衰し、指数減衰解は時間原点付近でシフトしている。さすがに看過できない。

これらの誤差を軽減するため、積分器基板だけPCBで作り直した。(元の基板はもったいないが廃棄処分)

基板上の配線長のみならず、基板とパネル間の配線長も最短になるよう工夫し、基板・パネル間配線は束ねずできるだけ距離を取り、SJ(電流加算点)のケーブルについてはGND電位に落としたアルミホイルでグルグル巻きにしてノイズ対策を行ってみた(途中で力尽きて一部しか処置しておりませんが…)。

下の写真は新たに製作した積分器基板である。

アナログスイッチAD7512の入手性が悪いので、念のためDG403でも代替できるように回路を組んだ。

2.4 出力セレクタ

下は演算器(積分器・加算器・乗算器)合計32個の出力から1つを選択する回路。

DG406というSP16Tアナログスイッチ(Digikeyで買ったがかなり高かった)を2つ使っており、選択中の演算器のアドレス(0~31)がフロントパネルのLEDにスタティック表示される。回路が少々冗長な気もしなくもないが、ブレッドボードでの実験ではきちんと動いていたのでこのまま採用した。押しボタンスイッチでアドレスをインクリメントして演算器の出力を選択する。

セレクタの実験の様子↓

完成した出力セレクタの基板たち(向かって右から2枚)↓

.jpg)

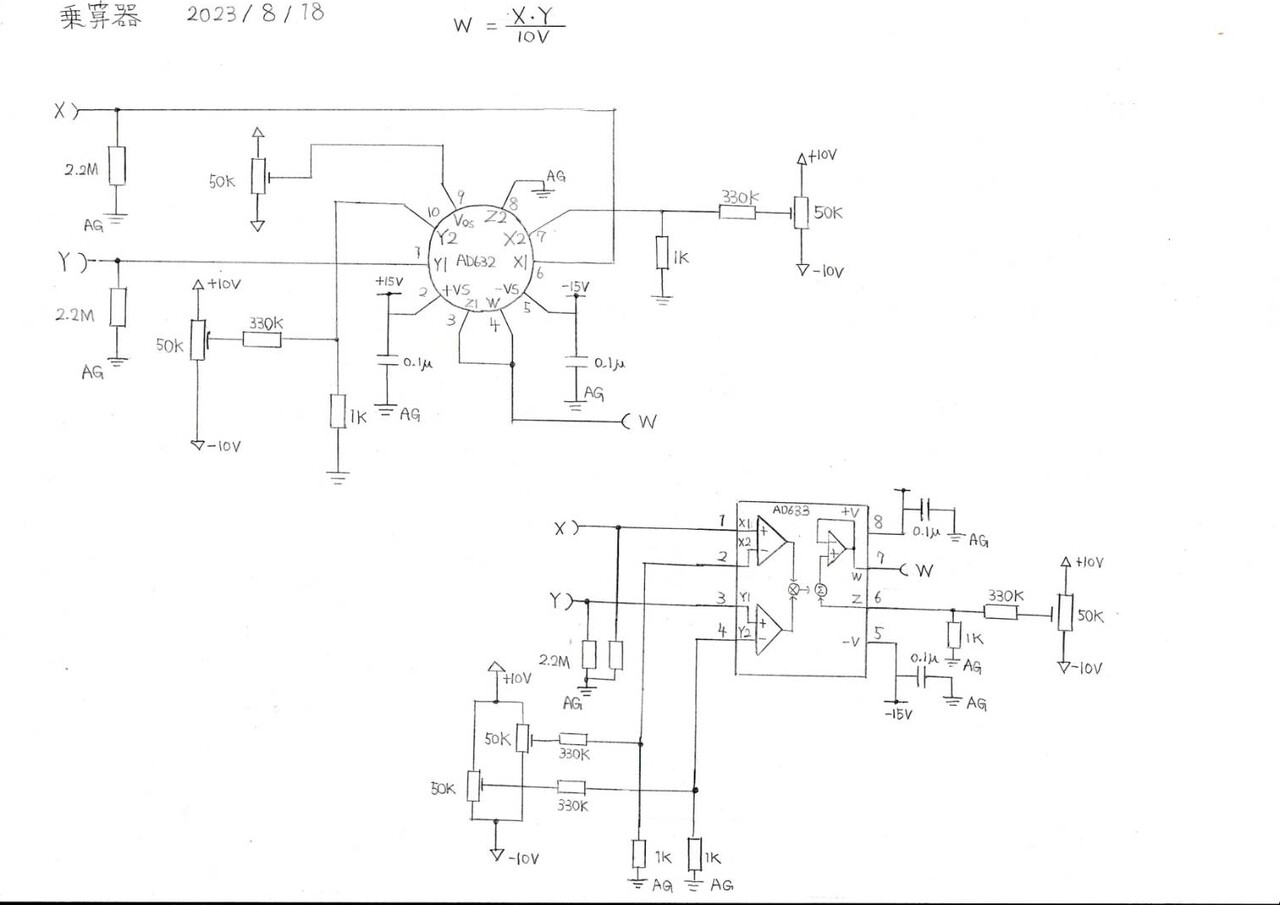

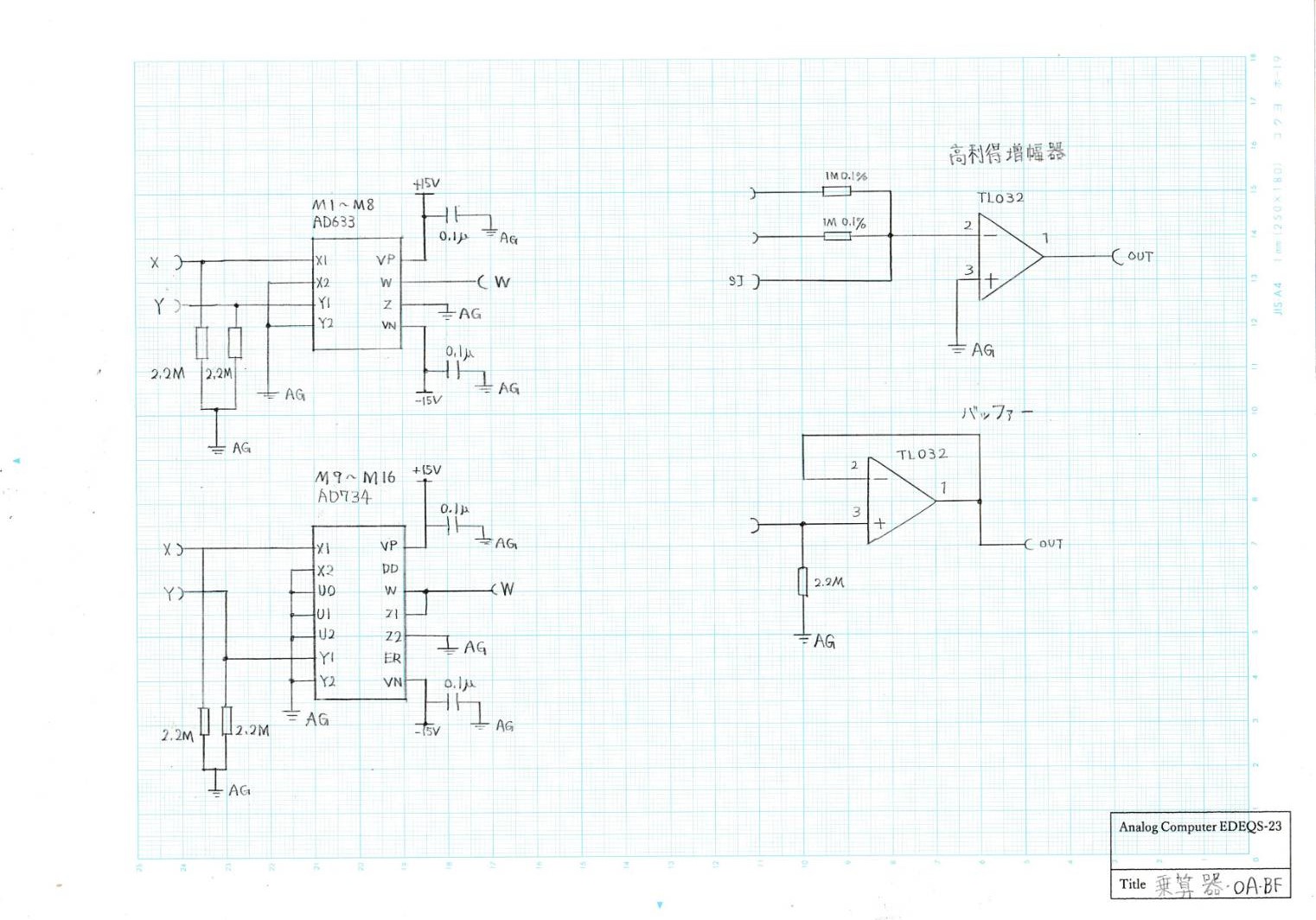

2.5 乗算器

当初の予定ではAD632、AD633を用いた乗算回路をそれぞれ8回路、合計16個用意する計画で、そのままだとオフセット電圧やフィードスルー誤差(一方の入力を0Vにしても出力が完全に0にならない現象)が残るので、トリマポテンショメーターを付加して調節できるようにするつもりだった。(下はそのトリム作業を想定して設計した回路)

しかし、AD633の実質誤差が無視できるほど小さく、さらに高精度乗算器AD734が手に入ったので、結局AD632とトリム回路を廃してAD633とAD734を採用した。最終的な回路は以下のようになった。

右の回路はバッファと高利得増幅器(オープンアンプ)である。バッファは受動インピーダンスによる演算回路の出力インピーダンスを改善し、高利得増幅器は乗算器をフィードバックループに挿入することで除算や逆関数の生成などを行える。乗算器の非線形誤差についてはアナログデバイセズ社のこのページに詳しいので参照して欲しい。

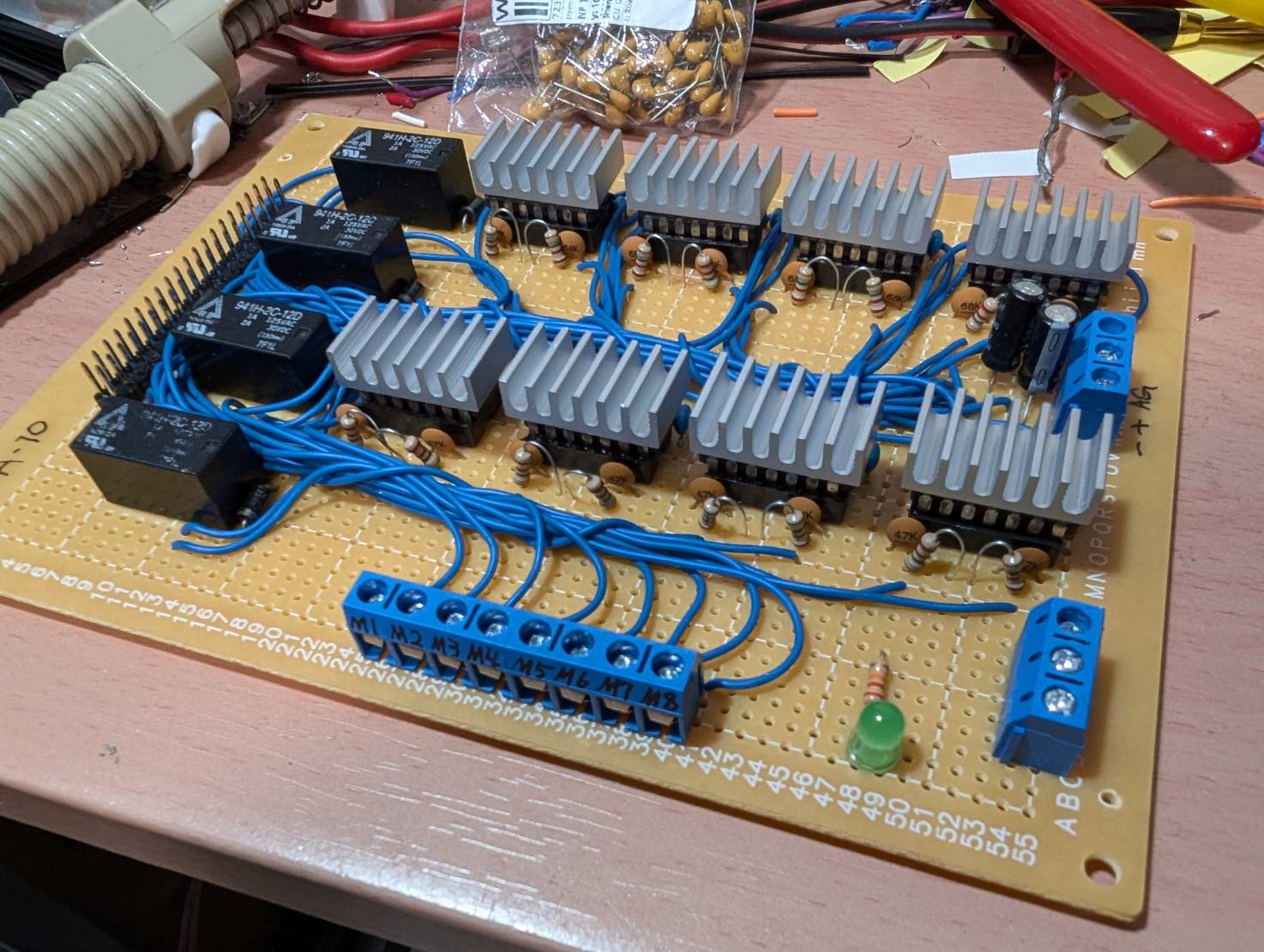

↓完成した乗算器基板

しかし何といってもこのAD734は恐ろしい程発熱する。(電源投入後数分で表面温度が35℃に…)ドリフトの増大など演算誤差の原因となるので、表面に両面接着型熱伝導テープを張り、その上に薄型ヒートシンクを取り付け、上からファンで空冷することにした。

2.6 絶対値/飽和要素

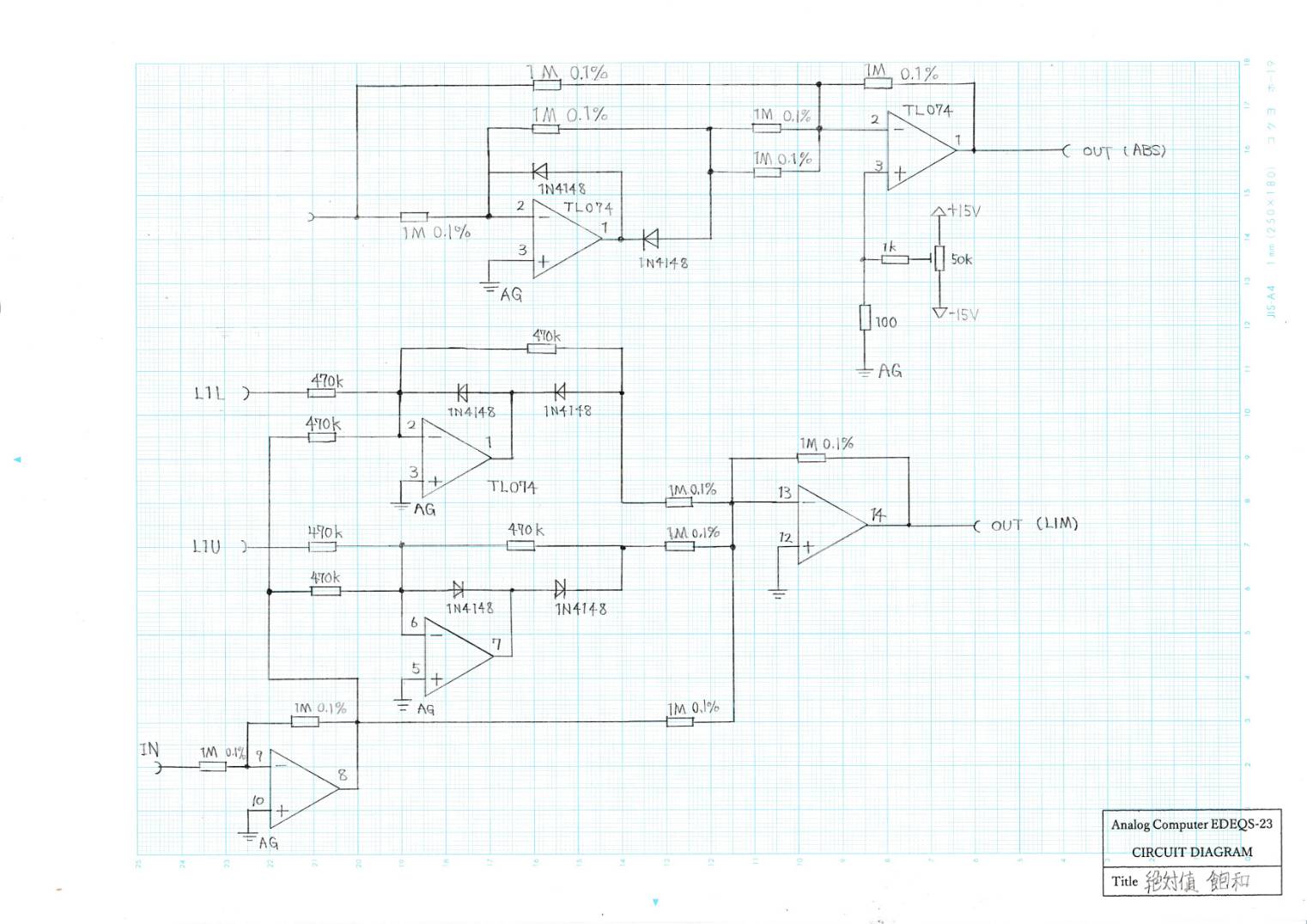

続いて絶対値要素と飽和要素。

絶対値要素は言うまでもなく入力の絶対値を出力する演算器で、オペアンプとダイオード(1N4148)による高精度全波整流回路である。飽和要素はクリップ回路であり、飽和特性の上限電圧と下限電圧は任意に設定できる。絶対値は4個、飽和要素は1個用意する。

2.7 比較器

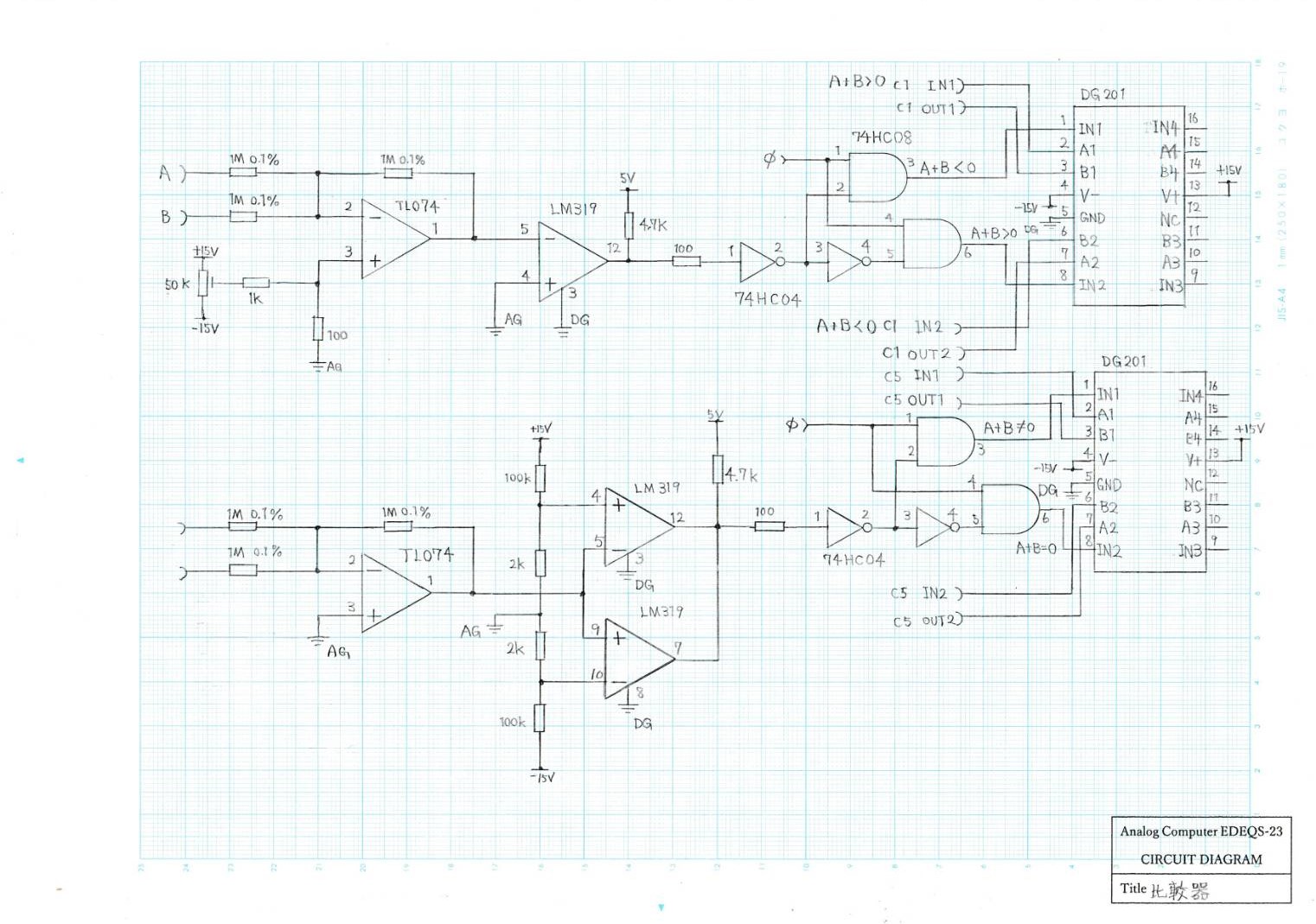

次は比較器。

上の回路の方は、2つの入力電圧A,Bについて、A+B>0ならIN1に加えた信号が、A+B<0ならIN2の信号が出力に現れる。下の回路はA+B=0の場合IN1が、≠0のときIN2が出力に現れる。A+B>0の回路は6個、A+B=0の回路の方は1個設ける。また、どちらも入出力端子とともにロジック出力(回路図上で言うとANDの出力信号)が前面パッチパネルまで導かれており、その信号を他の演算器(積分器のEXT-Hなど)で使うことができる。これにより、

\[f(x)= \left\{

\begin{array}{ll}

f_1(x) & \quad x>a_o \\

f_2(x) & \quad x<a_o

\end{array}

\right. \]

のような関数の場合分けが容易に実現できる。アナログコンピュータに不足している「条件分岐・判断」の能力を補うという意味で重要な演算器である。

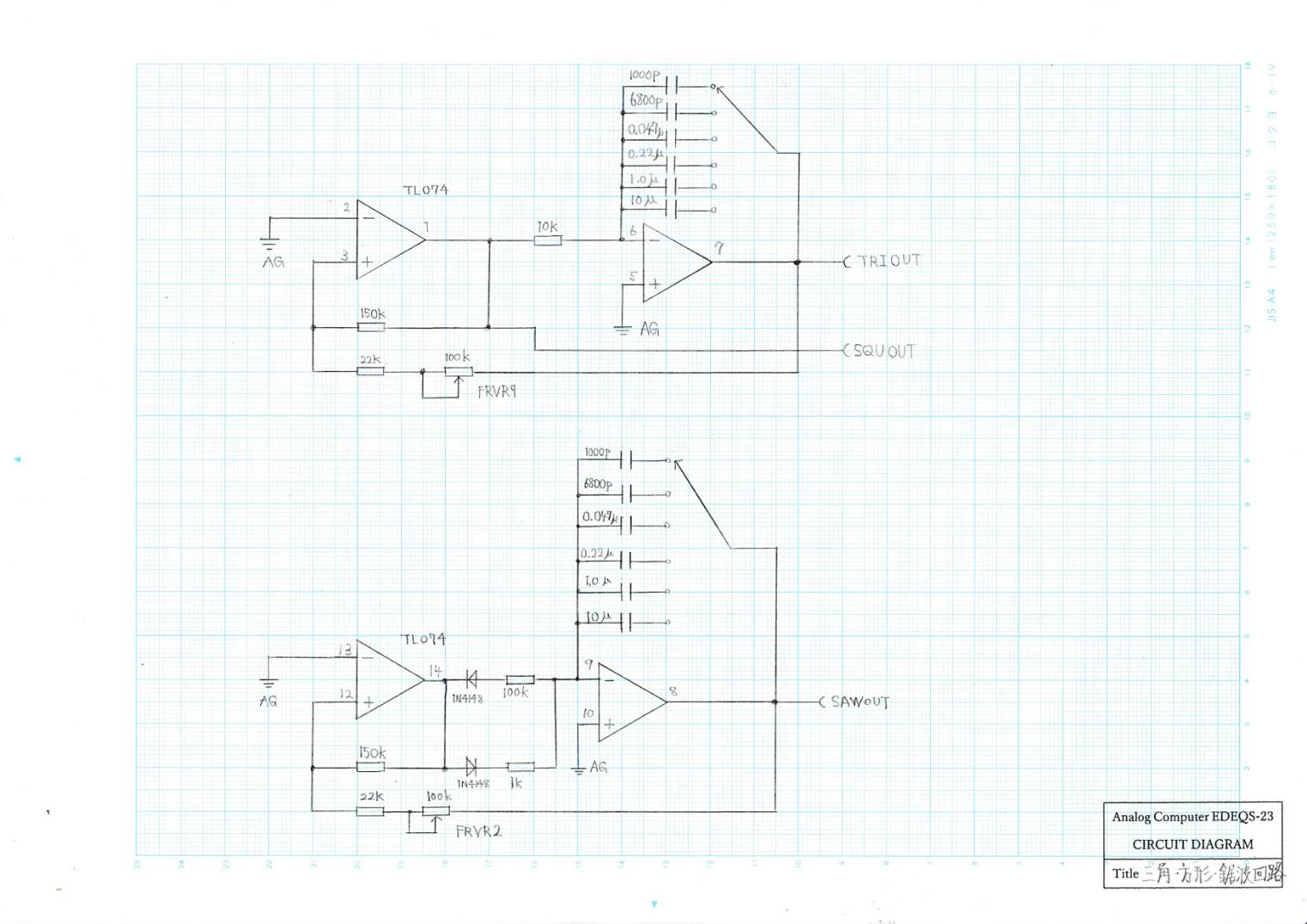

2.8 三角波・方形波・鋸状波発振回路

単純な発振回路。

積分器とヒステリシスコンパレータによる定番回路である。周期を変えると積分時定数が変わり出力振幅も同時に変化してしまうが、アナログコンピュータでは振幅の調整を他の演算器で容易に行えるので、特にAGC回路などは設けていない。

↓完成後の基板

2.9 係数器/メーター周辺

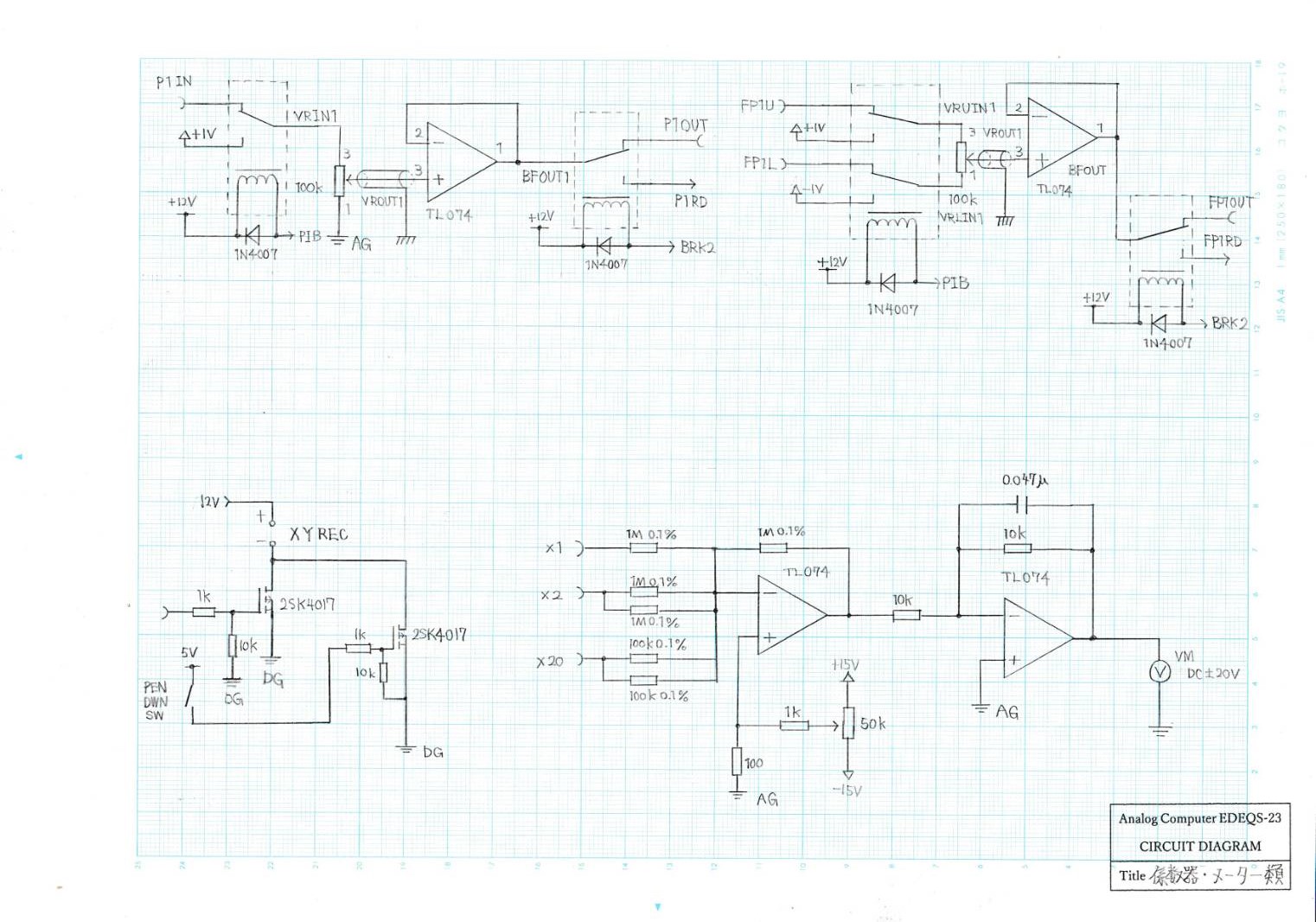

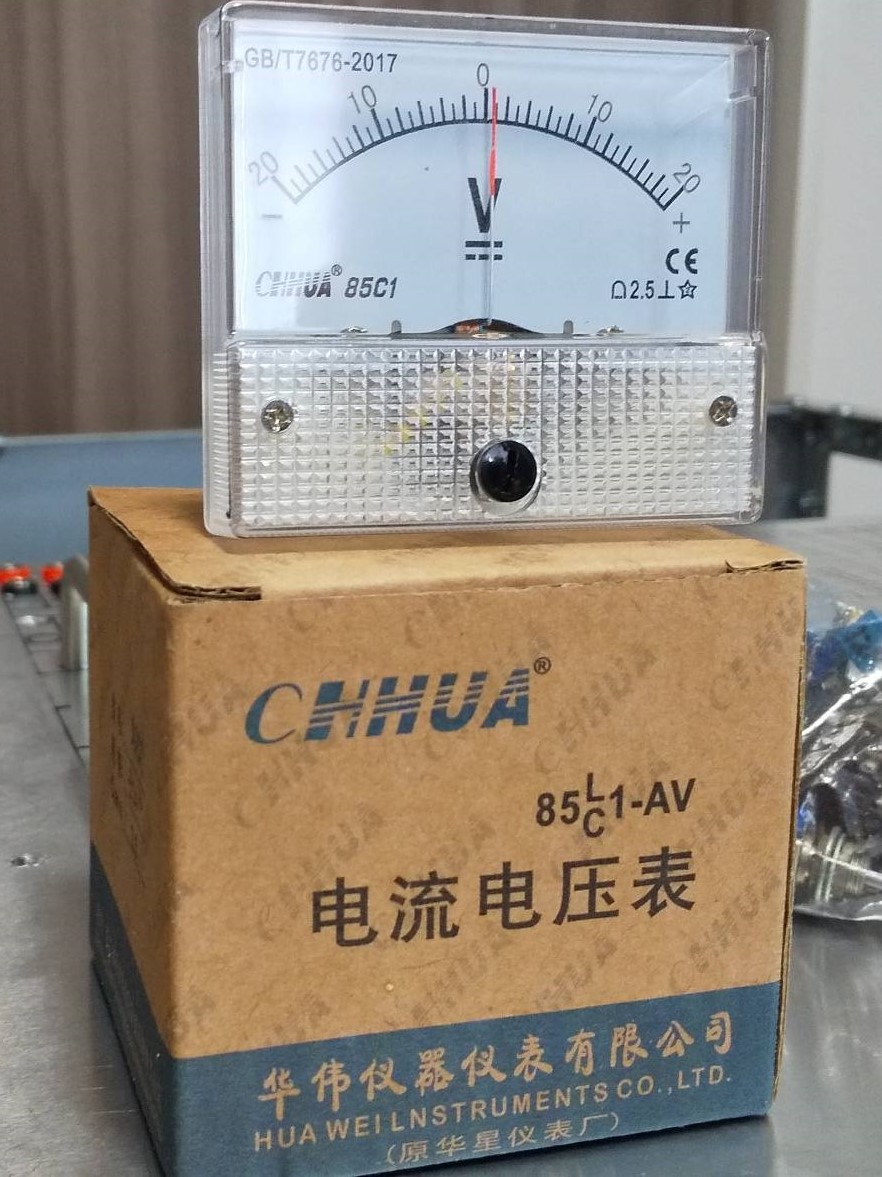

係数器とメーター駆動回路。

係数は10回転ポテンショメータで設定する。ボルテージフォロワによるバッファ回路を挿入して出力インピーダンスを上げて負荷効果による誤差を低減している。係数器出力はPOTSETモード及びBRKモードの時パネル部ジャックからリレーで切り離され、係数器セレクタ(ロータリースイッチ)に導かれる。係数器入力はPOTSETのときのみ内部高精度電圧(1V)に接続される。POTSETの時、セレクタで選択した係数ポテンショメータの設定値が電圧値として一つのバナナジャックに現れるため、係数の精密設定および設定値の検査が容易になる。通常の係数器(左上)は0~1の係数を設定できるが、右上の係数器は-1~+1の間の定数を自由に設定できる。積分器の初期条件を設定するのに便利である。

係数器基板の写真↓

回路図下の方はメーター駆動回路である。メーターは正負電圧どちらの表示もできる直流電圧計であり、低速モードで演算している時の解の変化をオシロスコープなしで見たいときに使うつもりである。この種の正負両用メーターは国内ではなかなか見つからなかったが、AliExpressで偶然見つけたので(少し高かったが)つい買ってしまった。

左下の回路はXYレコーダのペンの遠隔操作に使うちょっとした回路。

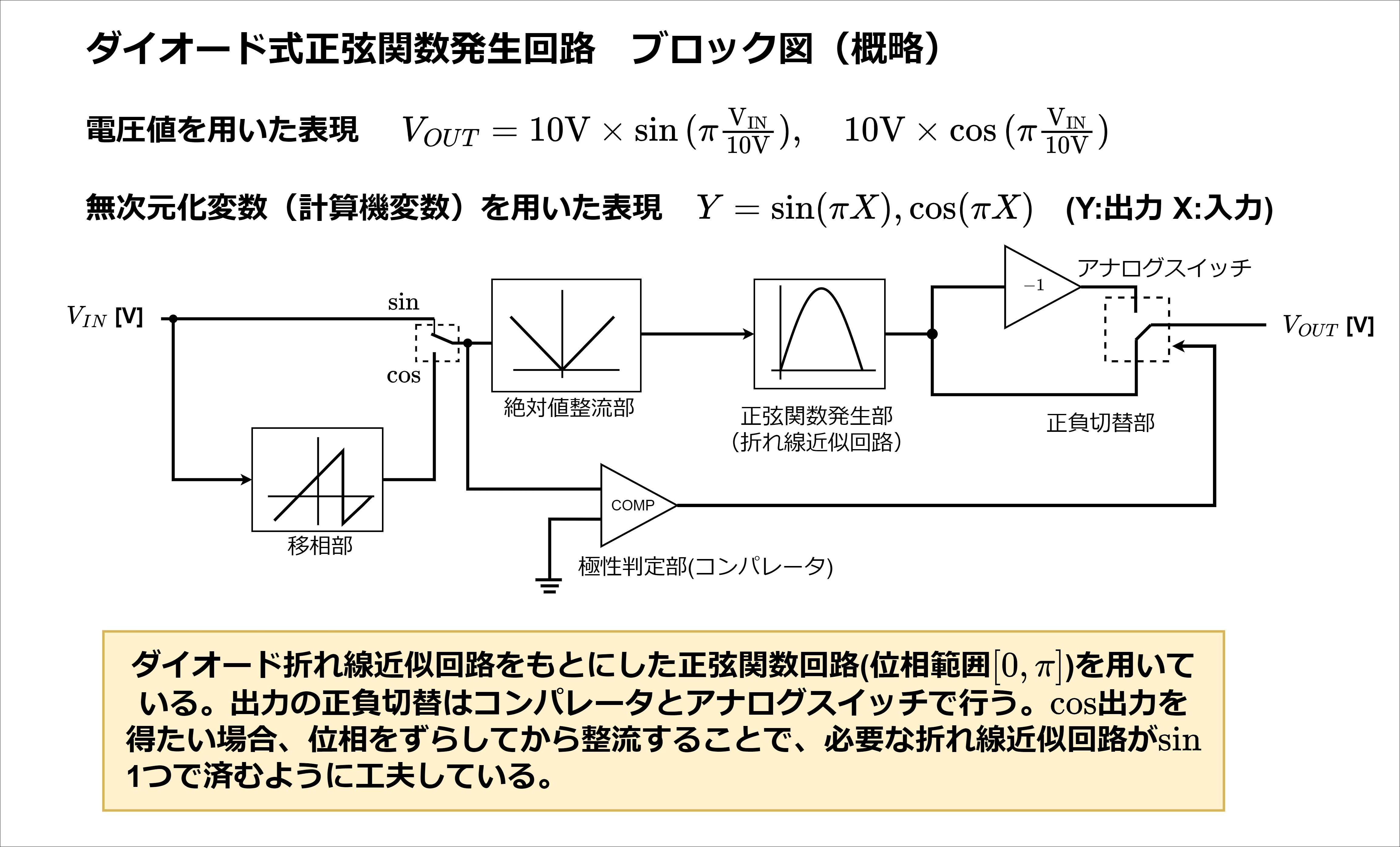

2.10 正弦・余弦・対数関数発生回路

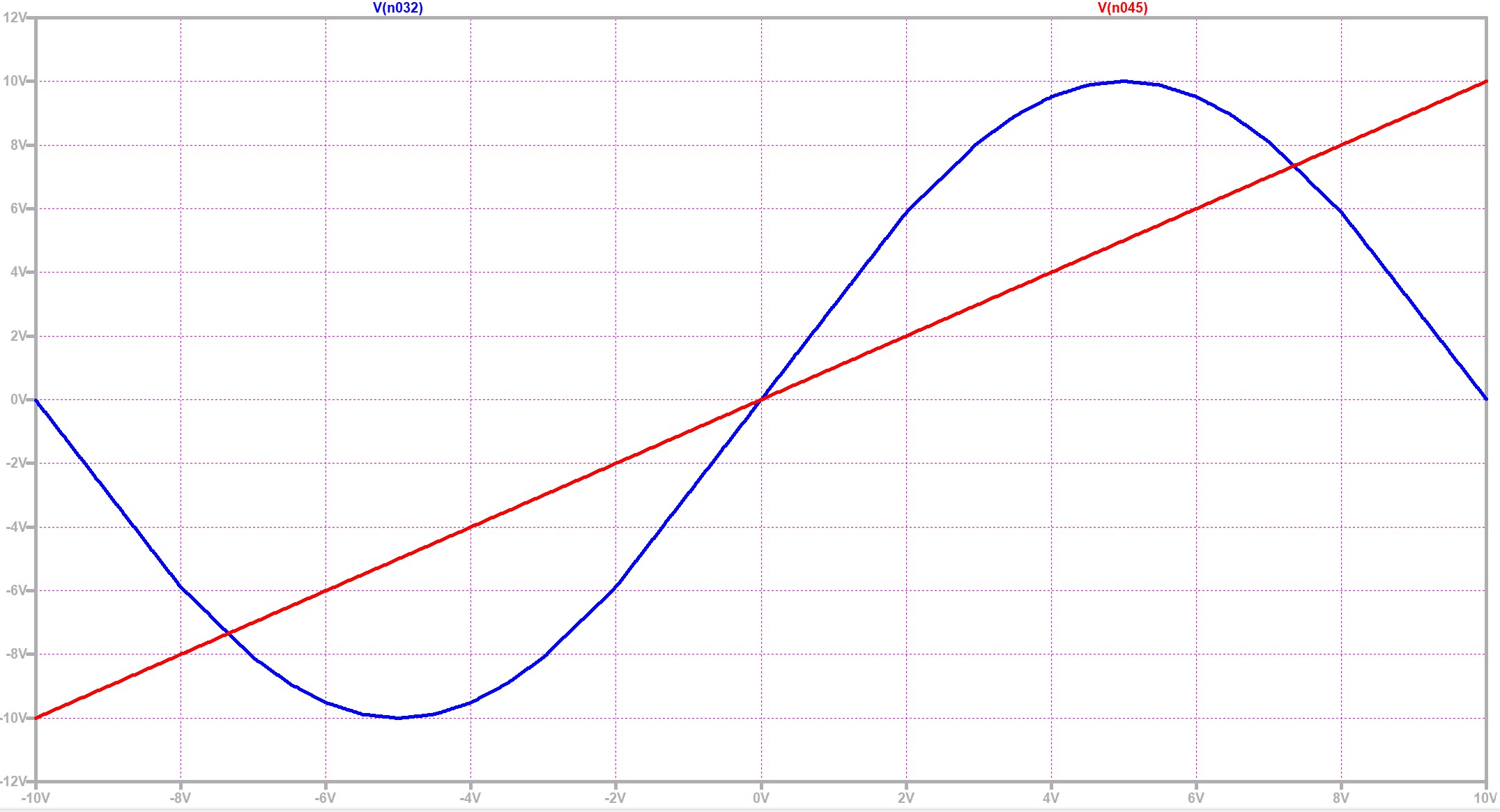

最後に関数発生回路も設置することにした。出力電圧が入力電圧の正弦(余弦)、または自然対数となる回路である。正弦関数回路はダイオードとオペアンプによる半波整流回路により電流加算を行う折れ線近似回路で\(\sin{x}\) の\(0<x<\pi\)を11点で近似する。スイッチの切り替えで余弦関数も発生できるようにしている。

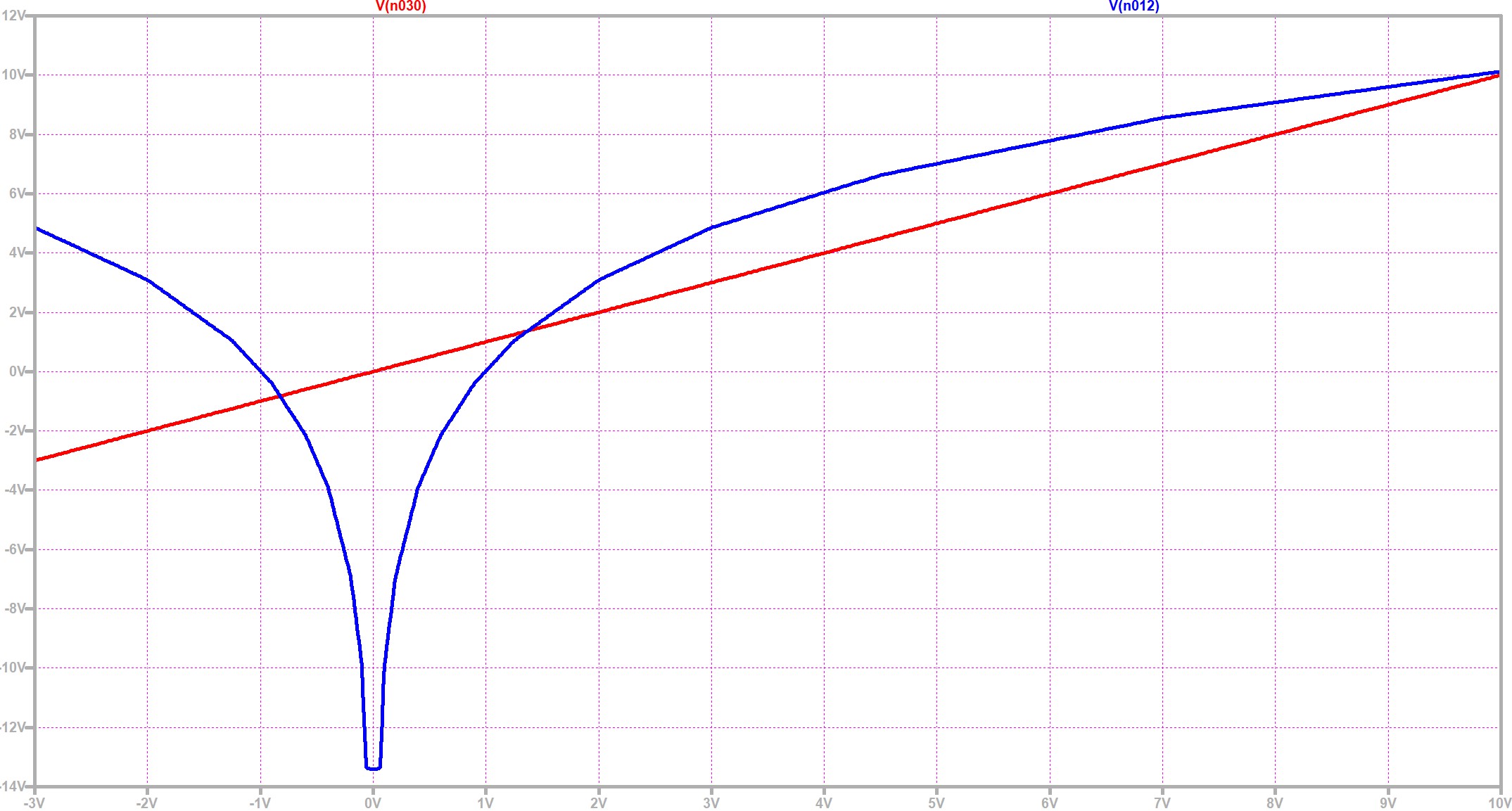

LTspiceでのシミュレーション結果 ↓

正弦関数などの偶関数は言うまでもなく原点対称であるから、折線近似点の数を半分にすることができ、回路規模も小さく抑えられる。

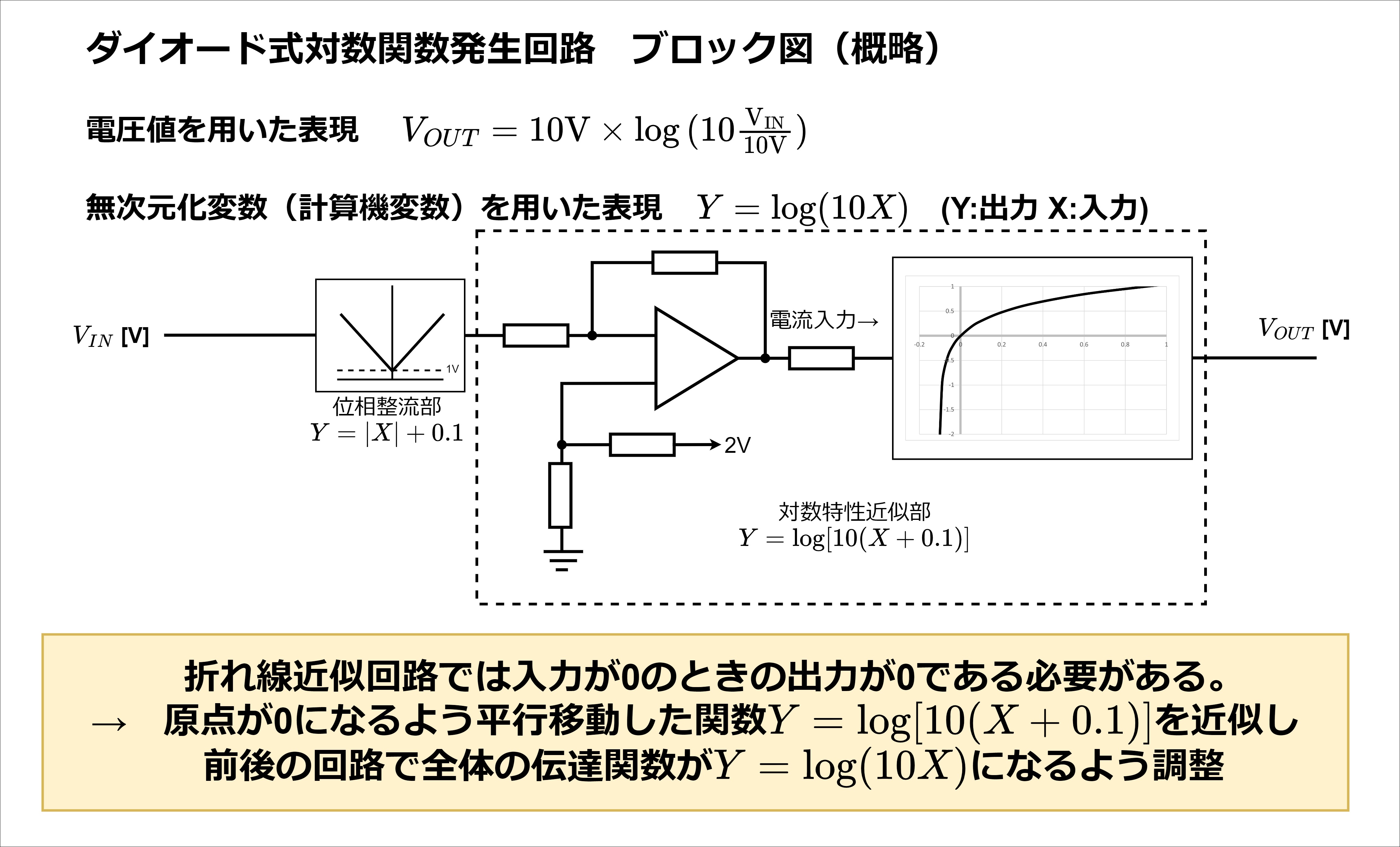

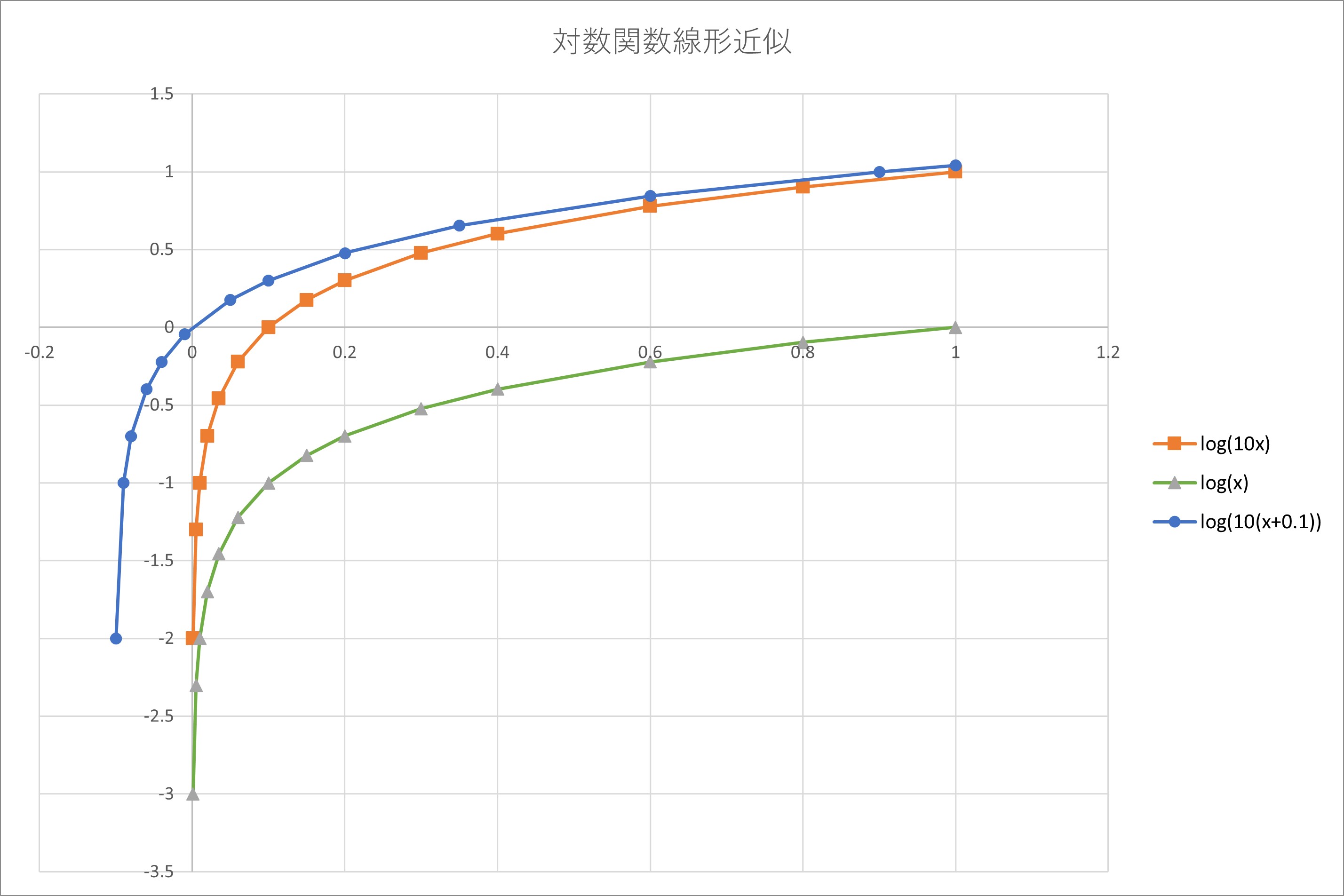

対数関数の方も同様の方式である。折れ線近似回路は入力0で出力も0である関数しか近似できないので、原点付近で負の無限大に発散する対数関数を直接実装できない。そのかわりに、0.1(=1V)だけ\(x\)軸負の方向に移動した曲線\(y=\log(10|x+0.1|)\)を線形近似しており、その近似回路の前の整流回路や定数加算回路で軸方向にちょこまかと平行移動して辻褄が合うようにしている。

最終的には\(y=\log(10|x|)\)(電圧値表示で\(V_{out}=10\rm{V} \log(10|\frac{V_{in}}{10\rm{V}}|)\))が対数回路の出力となる。

さすがにこの頃になるとユニバーサル基板で組む気力がなくなったので、JLCPCBにプリント基板を作ってもらった。

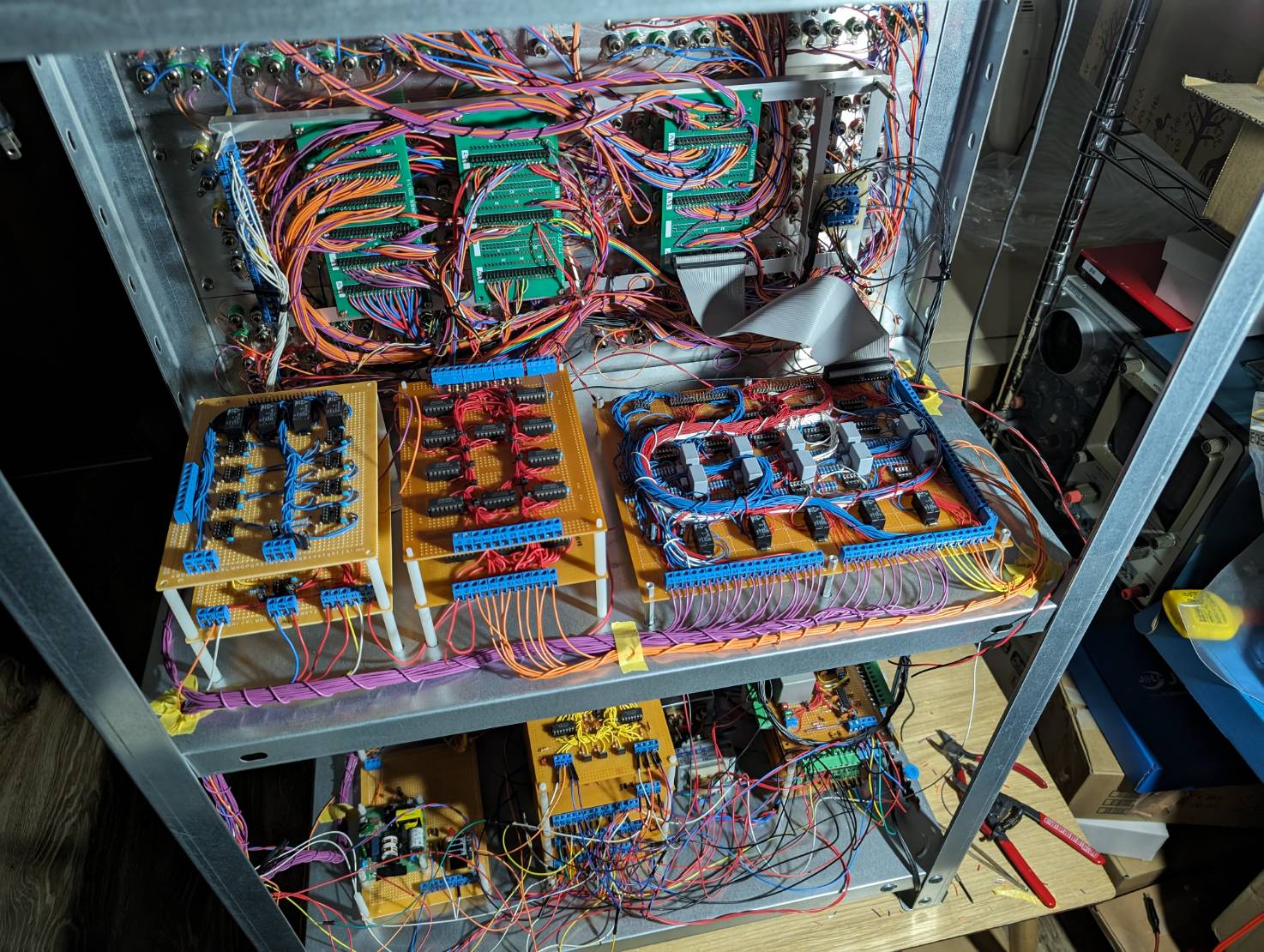

製作が完了した基板の一部↓ ユニバーサル基板をここまで大量に使うプロジェクトは初めてである。

3. 組み立て作業

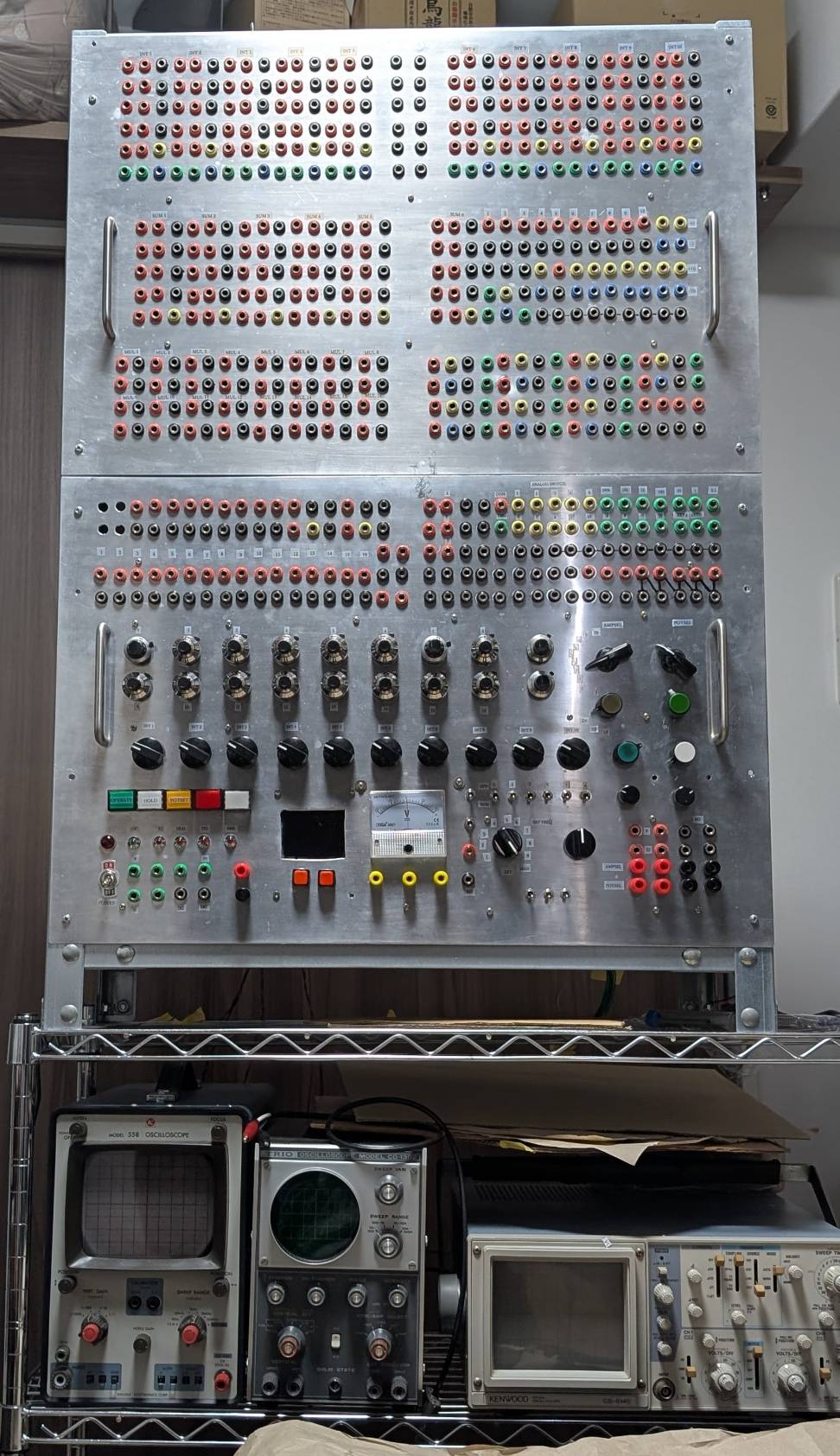

筐体は金属製のラック(Amazonで購入したもの)を流用した。これを骨組みに、パネルとして1.5mm厚のアルミ板を外側からねじ止めする形をとった。高さは90cm。

じつは筐体製作の方は基板設計が完了する前には既に取り掛かっており、1週間ほどのあいだパネルの穴あけ作業とポテンショメータやバナナジャック、スイッチ類の取り付け作業に明け暮れていた。ドリルでの穴あけ箇所が(正確な数は分からないが)700か所以上あり、さらに穴の直径も1cm大のものがほとんどなので、学生アパートの自分の部屋の中で作業するとかなりの騒音が長時間続くことになる。さすがにそれは下の階の人の迷惑になると思ったので、毎日大学に通い、部室の近くで場所とコンセントだけ借りて穴あけさせてもらった。

これが私のアルミ加工初体験となったのだが、まさか人生第一作目で1.5mm厚アルミ板に直径1cmの穴を数百箇所あけることになるとは思わず、穴あけ位置がずれたり、ドリルが板を嚙んで変形させたりと私の技術が未熟であるがゆえにいろいろ問題が発生したがまあ致し方なし。

この時点で私がやっているのは、「電子工作」というより「パネル上の端子と基板の間をひたすら配線する作業」と「アルミに穴をあける作業」であり、単調過ぎて。鬼も裸足で逃げ出すレベルの拷問ではあるが、これに耐えられるのも若さと趣味に対する情熱のおかげかもしれない(もしこれが仕事だったらモチベーションは3日も続かないだろう)

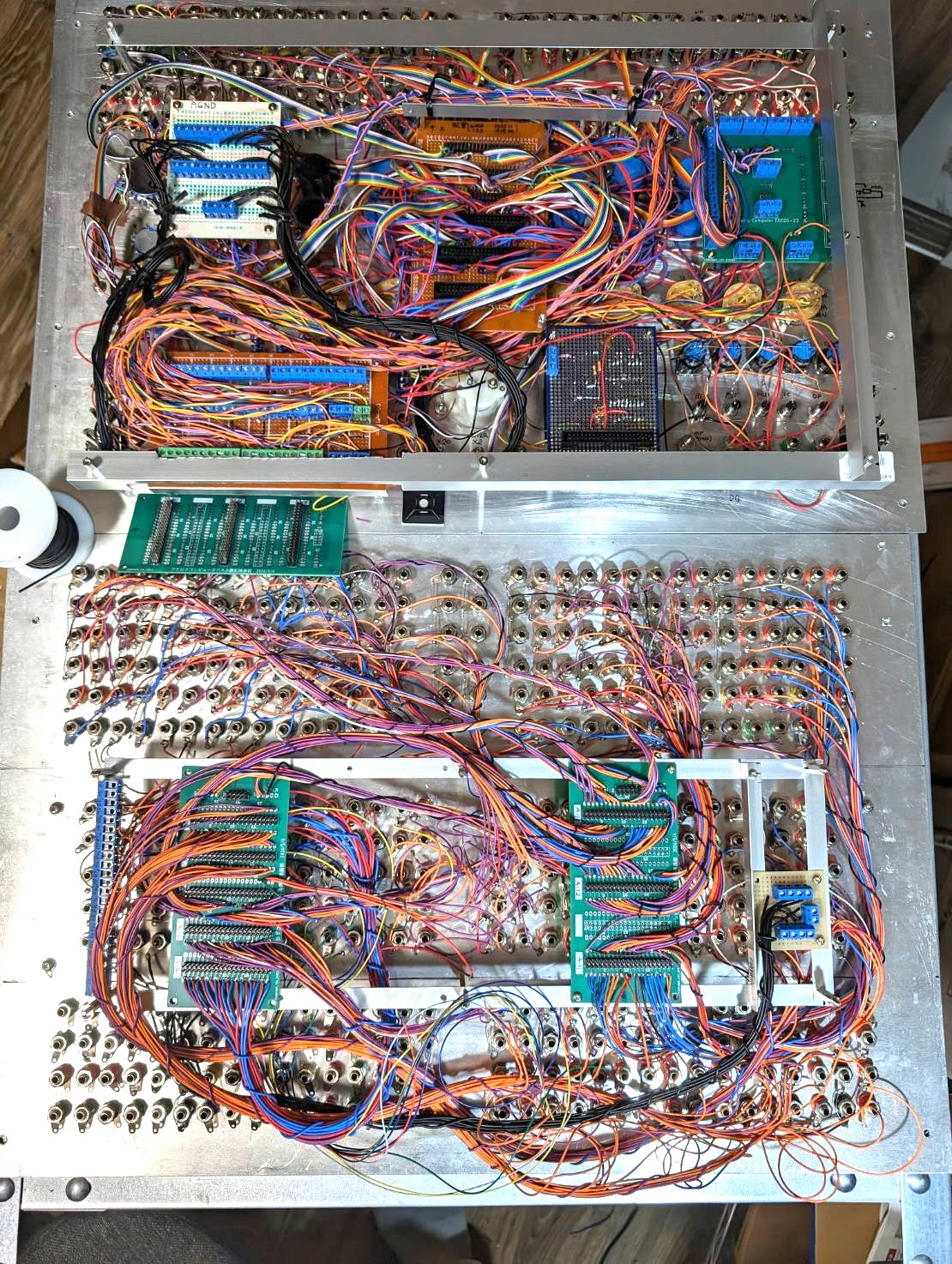

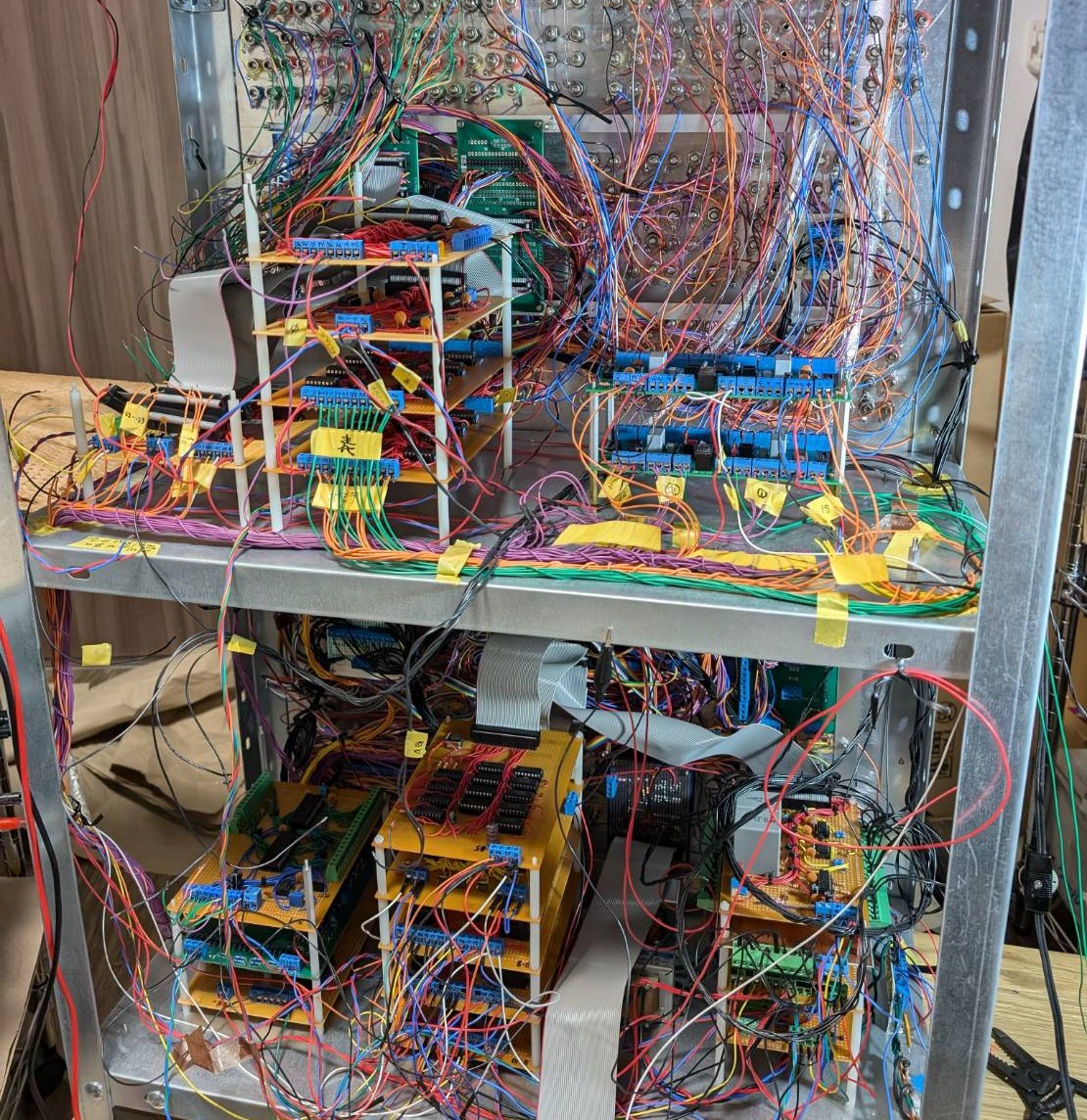

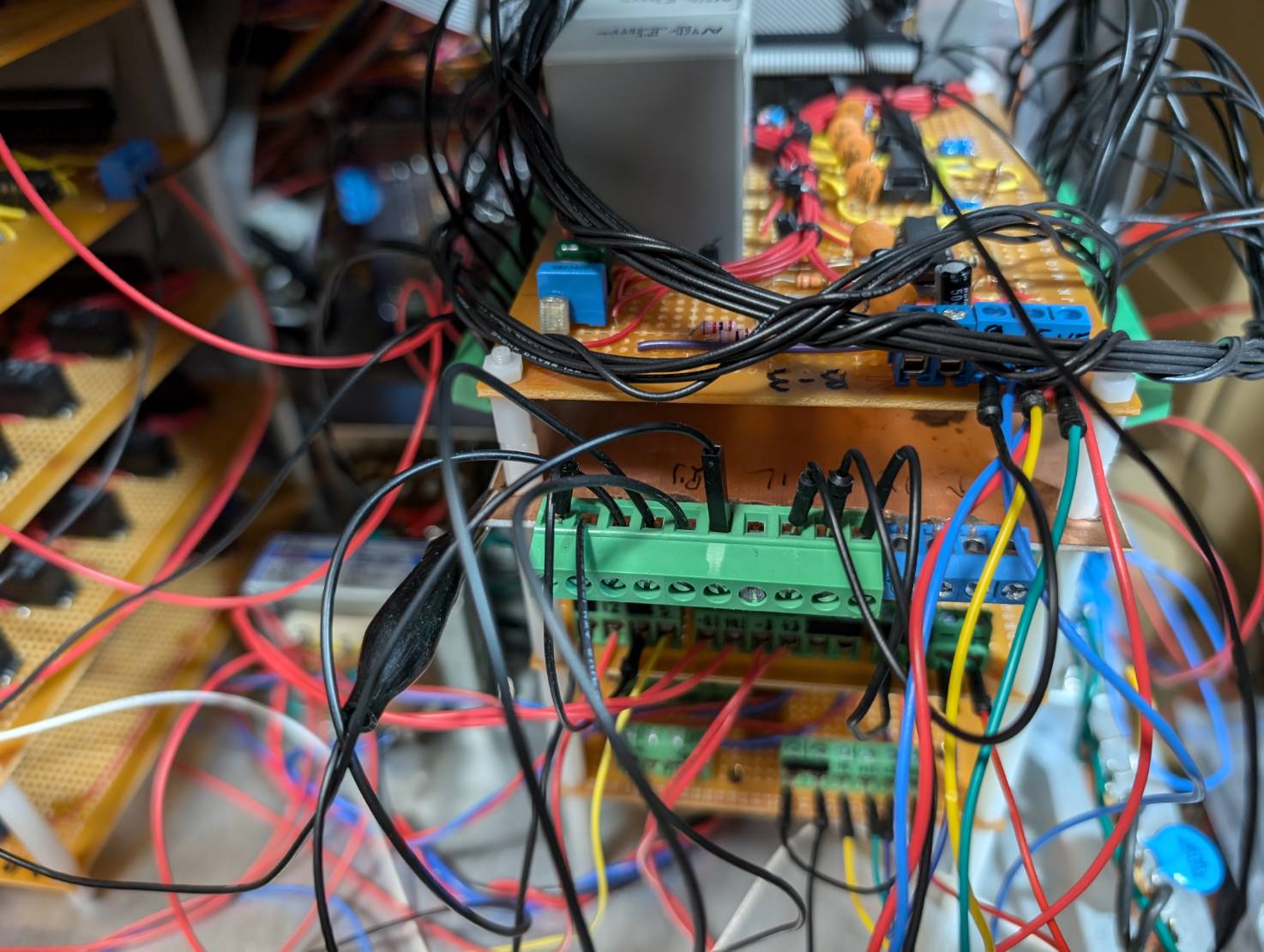

パネル裏の配線途中の様子↓

パネル裏側にアルミアングルと六角スペーサで枠を作り、配線の保持の役割と1.5mm厚しかないパネルに剛性を与える役割を担ってもらう。配線用基板にはフラットケーブル用ピンソケットとターミナルブロックが大量に並んでいるが、基本的に基板とパネルとの接続はフラットケーブルのみ。

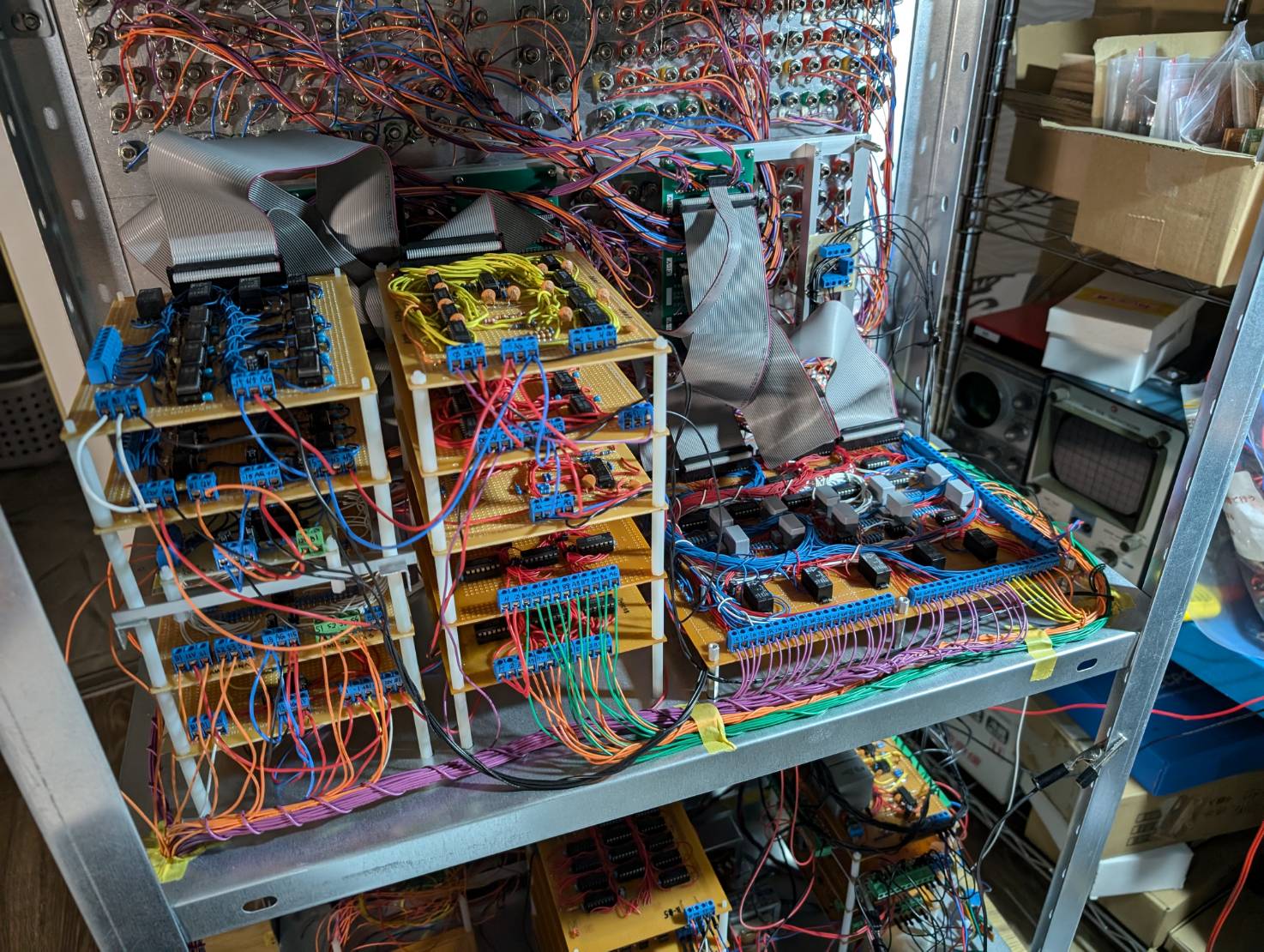

パネル側の配線の他に基板間連絡も必要である。ただひたすら回路図や配線図、自分の記憶を頼りに配線していく。半田ごてとテスターをとっかえひっかえしながら、いつ終わるかもわからない作業に没頭した。

↑ 2024年6月ごろの様子(この後不具合が発覚し大規模解体)

気持ち悪いくらいに配線が高密度に集積している。正直に言ってどの線がどの信号なのか把握しきれていない。高インピーダンス線とリレー用電源ラインなどを離すなどの最低限の配慮はしているが、色々なところがガバガバである。

下の写真は筐体下部に配置される銅張基板で、電源基板の真上、任意波形発生回路の下に配置されている。

一体何のための基板かと不思議に思われるかもしれないが、単なる1点GND用のベタ基板である。 計算機各所の全てのアナロググラウンドは全てここに配線され、電源回路の平滑コンデンサの足元でGNDに落とす。細かいところまでテレフンケンのアナログコンピュータのGND接続をパクった真似させてもらった。説明するまでもないが、GND線の共通インピーダンスをなくすことで演算の基準となるアナロググラウンドの電位を安定させる役割と、グラウンドループの形成を回避することでノイズが誘導されることを防ぐ役割がある。ノイズ対策の基本である。 1点GNDの欠点としてGND線の総延長が長くなることによる配線間の高周波結合が挙げられるが、演算信号周波数が高々1kHzなのであまり心配していない。 電源トランスは筐体下段に配置しており、重要な演算要素を格納している筐体上段とは距離があるうえ、両者はGND電位の棚板一枚で遮られているのでハムノイズが大きな問題になることはないと考えたが、念のためAC100Vラインもアルミホイルでシールドして低周波ノイズの低減も試みた。

筐体下部には何にも接続されてない高精度抵抗器、ダイオード、ツェナーダイオードを単体で配置している。積分器や加算器の入力端子を増設したり、ダイオード類を利用した非線形演算器(飽和要素、折れ線要素、不感帯要素、履歴要素 e.t.c.)を必要に応じて構成したりする場合に必要になる物である。

パネル部には「相平面セレクタ」も設置した。パネル部「X」「Y」「Z」の3つの端子に接続された3次元システム(ローレンツアトラクタなど)の信号を適切に選択して「XY平面」「YZ平面」「XZ平面」を出力するもので、オシロスコープで各相平面を表示させたいときに大変便利である。試作機の運用経験から、結線を組み替える手間を省きたかったため設置した。

4. 完成

構想開始から約1年後の2024年10月、当初の計画より半年以上遅れて完成した。試作機を含めると丸2年をアナログコンピュータ製作に費やしたことになる。

予算が足りず、裏面及び側面にねじ止めするはずだったアルミ板が用意できなかったので謎の仮材で間に合わせた。不格好ではあるが、自作アナログコンピュータはこれにて完成というわけです。(^^)/

今後の課題・目標

- 演算器出力の飽和警報回路の設置。

- 演算回路のエラーを自動でチェックする機能(dynamic check 及び static check)の設置。中期から後期にかけての高級商用アナログコンピュータにはこの機能が備え付けられているものもあった。

- 平方根・逆数発生回路の設置。乗算器と高利得増幅器で実現できるが、専用演算器があったほうが便利。

ただ、計算機本体(というか前面パネル)にもう余裕がないので、これらの機能は外付けするほかないだろう。